## <u>Altech Corp.®</u>

## **PCB Terminal Blocks**

#### **EXPANDED** - now with over 20,000 parts Selection & Styles visit altechcorp.com/PCBs

c**FL**us

PCB Plug-In

Connectors

Altech Corp.

#### Fixed

- Tubular Screw Clamp

- Screw-Cage Clamp

- Dual Pin Screwless Spring Clamp

#### Pluggable

• Tubular Screw Clamp Plug & Pin Headers

#### Mini Pluggable

- Screw-Cage Clamp Plug & Headers

Standard Pluggable

- Screw-Cage Clamp Plug

- Headers

- Double Level Headers

#### Spring Clamp Printed Circuit Board Terminal Blocks

#### Fixed Push-in PCB Terminals

- 2.50 / 2.54 / 3.50 / 3.81 / 5.00 /

- 5.08mm pin spacing

- 2A/ 6A/ 10A current rating

- 150V/ 300V

- Vertical/ horizontal

- Lever version

#### PCB Power Terminals Push-in

- 5.00 / 7.50 / 11.50mm pin spacing

- 20A / 35A current rating

- 300V

- Vertical/ horizontal

years

#### **Tension Spring Terminals**

- 2.50/ 2.54 / 5.00 / 5.08 / 7.50 / 10.00mm pin spacing

- 4A / 6A / 15A / 16A current rating

- 150V / 300V

PCB Fixed

Terminal Blocks

Altech Corp.

- Lever version

- Double level

#### Push-in Plugs

- 3.50/ 3.81 / 5.00 / 5.08mm

- pin spacing 10A current rating

- 300V

- Screw flange

#### *Complete line of Plug-In Connectors*

- All pin spacings

- Proven screw clamp design

- Compatible headers

#### Altech Corp.<sup>®</sup> Automation & Control Components 1984 - 2024 9

AltechCorp.com 908.806.9400

PCB Push-In / Spring Clamp Technology

## Electronic es THE AUTHORITY ON Ign **EMERGING TECHNOLOGIES** FOR DESIGN SOLUTIONS

**NOVEMBER/DECEMBER 2024** electronicdesign.com

## OPTIMIZING ANALOG CIRCUIT DESIGN USING

# Have you seen the industry's lowest-profile wirewound chip inductor?

## Hopefully the arrows help.

With a maximum height of just 0.28 mm, our new 0201HT Series is the industry's lowest-profile wirewound chip inductor, also featuring a tiny 0.58 x 0.46 mm footprint.

It offers up to 70 % higher Q and lower DCR than similarly-sized thin-film chip inductors and is optimized for high frequency impedance matching in applications such as cell phones, wearable devices, WiFi, Bluetooth, GPS and LTE/5G IoT networks.

The 0201HT provides SRF as high as 36 GHz and is available in 14 inductance values from 0.5 to 13 nH.

Find out why this tiny part stands so tall. Download the datasheet and order your free samples today at ...

www.coilcraft.com

## Electronic Design.

## **IN THIS ISSUE**

#### **FEATURES**

8 Adopting AI-Based Circuit Optimization and Migration

> Analog designs are challenging, but artificialintelligence optimizations are improving and speeding up the design process.

12 So... What if THAT Analog Computer was Cheaper than a Smartphone? (Part 1)

> A "cheap as chips" open-source Analog Computer can run circles around a Raspberry Pi in solving differential equations and for simulating natural phenomena.

16 Undergrad EE Students Await Their Newborn TI-Fabbed Chip Designs

Georgia Tech's ECE undergrads design custom mixedsignal ASICs that are fabricated by Texas Instruments on 300-mm wafers and returned for testing.

20 So...Analog Computing Hits a Bump in the Road and All THAT (Part 2)

Editor Andy Turudic uses THe Analog Thing Analog Laptop Computer to simulate an automobile suspension encountering a pothole.

- 26 New Memories Making Meaningful Strides Non-volatile technologies like MRAM and particularly ReRAM are poised to finally take a major leap into the embedded-memory design space.

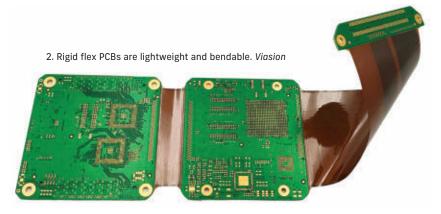

- 28 **Top 5 Challenges in PCB Assembly** In Part 1, we explore the benefits of miniaturization and the five main challenges it introduces in PCB assembly.

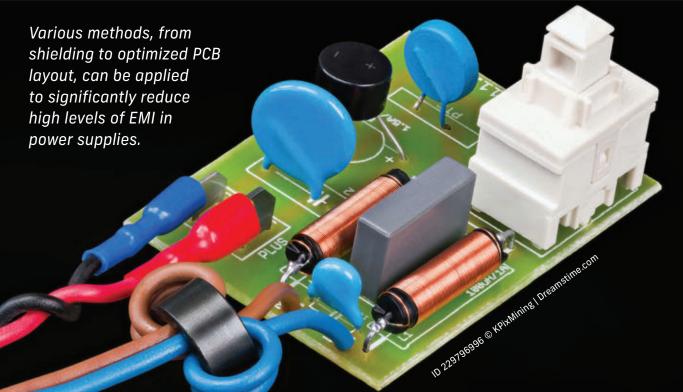

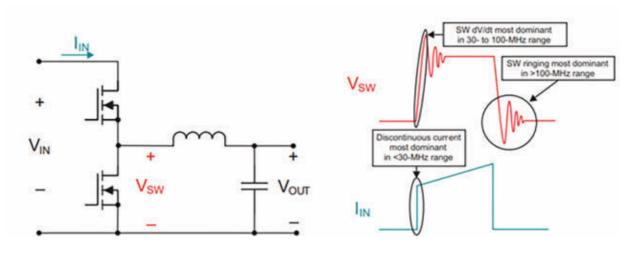

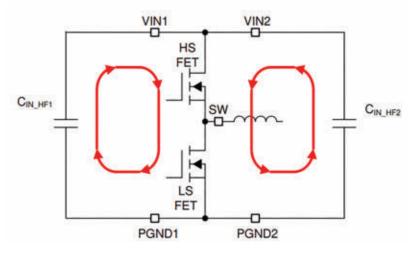

- 31 Minimize the EMI in Your Power Supplies Various methods, from shielding to optimized PCB layout, can be applied to significantly reduce high levels of EMI in power supplies.

#### **COLUMNS & DEPARTMENTS**

- Editorial Electronic Design's Focus Amid Changing Times

- 5 Ad Index

4

- 6 Watch & Connect

- 40 Lab Bench Peripheral Connections for Prototyping

Cover image: Naphat Ittipong\_1618844113 | iStock / Getty Images Plus

#### THIS NOVEMBER/DECEMBER

**ISSUE** of *Electronic Design* wraps up over 70 years of regular print and then PDF versions of our issues, which subscribers have been reading over all these years. Our 75th anniversary will be in 2027.

*Electronic Design* has had an online digital focus for a long time. We have more articles than would fit into the print issues since I started with *Electronic Design* in 2000. We picked the best to go into the print edition and lately the PDF version. Physical print issues went away a while ago. It's just too expensive to print and ship these days, and most readers are using our website already. The number of readers has always been higher due to our limited subscription base.

#### Finding New Content on Electronic Design

As with most publications, we have a host of *Electronic Design* newsletters

#### Editorial BILL WONG | Senior Content Director

## **Electronic Design's Focus** Amid Changing Times

From special reports to audience surveys, Electronic Design is going all digital all the time. Editorial Director Bill Wong dives into the publication's plans.

that provide regular notification of new articles. Those interested in similar functionality to our PDF issues should check out our Top Stories of the Week. These are collections of the articles we have on the website for the week just in case you miss one, or if you prefer to scan the list rather than receiving a newsletter. Of course, you can do both as the newsletters tend to be a targeted subset for topics like power or automotive.

Top Stories of the Week is handy, but it only groups things by date. So, what we've been doing over the last few years is building our curated TechXchanges. These focus on a topic and incorporate new articles as they arrive, as well as collect evergreen content that *Electronic Design's* editors have chosen as useful for the topic.

TechXchanges are more focused than our technology channels like Analog and AI/ML. These list all of the articles for the

Electronic Design's TechXchanges provide a curated list of articles on a particular topic that readers should find useful. ID 30131704 © Luchschen | Dreamstime.com

topic with the most recent ones residing at the top, but the subject matter is typically very broad.

One example is the Engineer's Guide Oscilloscope Techniques (see figure). This is actually an overarching TechXchange that groups more detailed subcategories into their own separate TechXchanges, like Choosing an Oscilloscope and What's the Difference: Oscilloscopes. You can also leave suggestions for additional articles as we continue to update the TechXchanges with new content as it arrives.

#### More Feedback and Research Reports

Many of you are probably familiar with our Annual Salary Survey and our Quick Polls. These have provided us with your insights, which was not possible with our print issues.

Our latest, "Is Mixing AI with Software Tools and Development a Good Idea?," includes a survey that we hope you will take. It will provide us with more insight into how everyone is using artificial intelligence and machine learning (AI/ML) in the design cycle rather than embedding it into a product.

We're looking forward to our 75th anniversary and providing readers with the latest articles, podcasts, and videos on existing and emerging topics relevant to *Electronic Design* engineers, programmers, and managers.

#### NANO Nuclear's 5-MW Electricity Generator in a Shipping Container

**INSANE LEVELS OF** electrical power are needed to support AI in data centers, and the electrification of mobility means development of remote locations for the extraction of critical mineral resources. This includes the powering of fully electric 1-MW mining trucks.

A number of startups are developing small modular reactors (SMRs) in the 20- to 500-MW power output range, requiring extensive site development, construction, and support resources. However, NANO Nuclear Energy Inc. (NASDAQ:NNE) is uniquely positioned in the micro-reactor space with two commercial micro-reactor designs that output up to 5 MW, integrating them with the complete electrical generator housed in an ISO shipping container.

In this podcast, we discuss markets, applications, Red October "caterpillars," engineering design, and operational considerations of these micro-reactor systems with our guest, NANO Nuclear's CEO, James Walker.

#### AD INDEX

| ABC TAIWAN ELECTRONICS CORPORATION | 25    |

|------------------------------------|-------|

| ALTECH CORPORATION                 | 0     |

| COILCRAFT, INC                     | 2     |

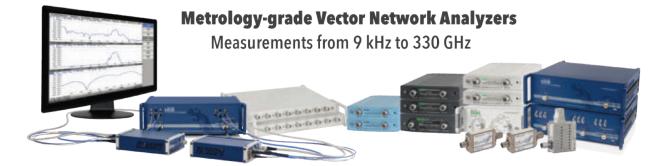

| COPPER MOUNTAIN TECHNOLOGIES       | 38-39 |

| KEYSTONE ELECTRONICS CORP          | 15    |

| KOA SPEER ELECTRONICS, INC.        | 23    |

| PICO ELECTRONICS INC               | 34-35 |

| ROCHESTER ELECTRONICS, INC         | 36-37 |

| TAEJIN TECHNOLOGY CO., LTD.        | 11    |

| YUAN DEAN SCIENTIFIC CO., LTD.     | 7     |

|                                    |       |

#### FOLLOW US ON FACEBOOK AND TWITTER

(ElectronicDesign)

(@ElectronicDesgn)

#### Electronic Design.

#### EDITORIAL

Market Leader - Electronic & Mechanical Group: **Michelle Kopier**, *mkopier@endeavorb2b.com*

Senior Content Director: Bill Wong, bwong@endeavorb2b.com Executive Editor: David Maliniak, dmaliniak@endeavorb2b.com Managing Editor: Roger Engelke, rengelke@endeavorb2b.com Editor-at-Large: Alix Paultre, apaultre@endeavorb2b.com Senior Editor: James Morra, jmorra@endeavorb2b.com Technology Editor: Cabe Atwell, catwell@endeavorb2b.com Technology Editor: Andy Turudic, andyt@endeavorb2b.com

#### **CONTRIBUTING EDITORS**

Lee Goldberg, Bill Schweber, Murray Slovick, Steve Taranovich, Alan Earls

#### ART DEPARTMENT

Group Design Director: Anthony Vitolo, tvitolo@endeavorb2b.com Art Director: Jocelyn Hartzog, jhartzog@endeavorb2b.com

#### PRODUCTION

Production Manager: Brenda Wiley, bwiley@endeavorb2b.com Ad Services Manager: Deanna O'Byrne, dobyrne@endeavorb2b.com

#### AUDIENCE MARKETING

User Marketing Manager: **Debbie Bouley** dbouley@endeavorb2b.com Article Reprints: reprints@endeavorb2b.com

#### SUBSCRIPTION SERVICES

OMEDA, 847-559-7598 or 877-382-9187 electronicdesign@omeda.com

#### LIST RENTAL

List Rentals/Smartreach Client Services Manager: Kelli Bery, kberry@endeavorb2b.com

#### SALES & MARKETING

Gregory Montgomery, gmontgomery@endeavorb2b.com AZ, NM, TX

Samantha Nelson, snelson@endeavorb2b.com AL, AR, SOUTHERN CA, CO, FL, GA, HI, IA, ID, IL, IN, KS, KY, LA, MI, MN, MO, MS, MT, NC, ND, NE, OH, OK, SC, SD, TN, UT, VA, WI, WV, WY, CENTRAL CANADA

Elizabeth Eldridge, eeldridge@endeavorb2b.com CT, DE, MA, MD, ME, NH, NJ, NY, PA, RI, VT, EASTERN CANADA

Stuart Bowen, sbowen@endeavorb2b.com AK, NORTHERN CA, NV, OR, WA, WESTERN CANADA AUSTRIA, BELGIUM, FRANCE, GERMANY, LUXEMBURG, NETHERLANDS, PORTUGAL, SCANDINAVIA, SPAIN, SWITZERLAND, UNITED KINGDOM

Diego Casiraghi, diego@casiraghi-adv.com ITALY

Helen Lai, helen@twoway-com.com PAN-ASIA Charles Liu, liu@twoway-com.com

#### PAN-ASIA

VP of Digital & Data Innovation: Ryan Malec, rmalec@endeavorb2b.com

#### **ENDEAVOR BUSINESS MEDIA, LLC**

30 Burton Hills Blvd, Ste. 185, Nashville, TN 37215 | 800-547-7377 www.endeavorbusinessmedia.com

CEO: Chris Ferrell

COO: Patrick Rains CRO: Paul Andrews

Chief Digital Officer: Jacquie Niemiec

Chief Administrative and Legal Officer: Tracy Kane

Chief Marketing Officer: Amanda Landsaw

EVP, Design & Engineering Group: Tracy Smith

@ www.electronicdesign.com

#### Video ► Examining EV Charging Infrastructure Issues

Electric vehicles (EVs) run on batteries that require periodic charging. A charging infrastructure is required to provide this power. In general, the deployment and maintenance of a national EV charging system is almost more challenging than the technology behind EVs and their batteries.

*Electronic Design* Content Director Bill Wong talked with Jeff Postelwait, Managing Editor at tdworld.com, and Janelle Penny, Editor in Chief at buildings.com, about some of the issues associated with building out such an infrastructure. *www.electronicdesign.com*/55238763

#### Video Toshiba's New Ownership and Future

Toshiba was delisted last year after 74 years on the Tokyo exchange, following a decade of troubles for the company. The entity was taken private by a group of investors led by private equity firm Japan Industrial Partners.

The \$14 billion takeover has the interest of Japan's government, as the company employs over 100,000 people and its operations are seen as critical to national security. In this video, we talk with Armin Derpmanns, VP of Marketing and Operations for Toshiba Electronics Europe, about the future of the company. *www.electronicdesign.com*/55241434

#### 2024 Engineer's Holiday Gift Guide

Our editors offer up some gifts that are fun, practical, and affordable for the fulltime or budding engineer. You may wind up buying one of these suggestions for yourself.

www.electronicdesign.com/55238690

#### How RTK Can Help Autonomous Vehicles See the World

AVs can't become fully reliable until they precisely know their location. Here's how real-time kinematic integration provides the accuracy needed to propel self-driving tech forward.

www.electronicdesign.com/55242976

#### How to Model, Measure, and Reduce EMI Noise

Electromagnetic-interference disturbances are becoming more intense due to more complex and powerful designs. Engineers can take several courses of action to tamp down the noise.

www.electronicdesign.com/55237516

### **DC-DC Converters**

0.25W~150W 1" x 1"/ 2" x 1"/Half-Brick SIP/SMD/DIP Package

#### Recommended >

**Compact Size** 0.94" x 0.54"

Ultra-wide 10:1 Input

8:1 Wide Input Range

#### **LAN Filters RJ45** Connectors

Inductor Pulse Transformer

Telecom Transformer

**High Frequency Transformer**

1xN.2xN Port 1G/2.5G/5G/10G Base-T with PoE+/PoE++

#### **AC-DC Converters**

0.5W~300W SIP/DIP Package Module/Open Frame

## **CONTACT US**

No.61, Keji 3rd Rd., Annan Dist., Tainan City 70955, Taiwan TEL:+886-6-3842899 FAX:+886-6-3843288 E-mail: info@yds.com.tw Website: www.yuandean.com

## Adopting AI-Based Circuit Optimization and Migration

Analog designs are challenging, but artificial-intelligence optimizations are improving and speeding up the design process.

**THE USE OF** artificial intelligence (AI) has gained significant traction in many domains of EDA, and for good reason. AI learns from experience, adapts, and converges on a solution while considering conflicting goals with complex tradeoffs.

Such characteristics make AI highly valuable in tackling many of EDA's hardest challenges, where traditional optimization approaches—either manual or algorithmic—are either sub-optimal, too slow, or fail altogether. AI has the potential to revolutionize the way we design, optimize, and, in particular, migrate analog designs.

#### Traditional Optimization Approaches Fall Short

Advances in EDA algorithms have made it possible to scale digital chips to the size of billions of transistors. The scaling of digital design automation builds on abstractions of digital signal levels (1s and 0s) and synchronous operation (discrete time), allowing for a divide-and-conquer approach. Analog design, on the other hand, doesn't benefit from such abstractions. Individual elements of the design influence each other in complex interactions, making it impossible to optimize one part of the circuit without affecting others. Also, the design metrics are complex, as designers need to consider dozens of metrics, such as supply current, signalto-noise ratio, jitter, hysteresis, slew rate, CMRR, DC gain, and more across hundreds of process corners.

Due to these inherent complexities, analog design has remained a largely manual process. This puts severe limits on the potential to exploit the multitude of specialized sub-nodes made available from foundries to take advantage of market opportunities. To understand why this is so, let's look at where traditional optimization approaches fall short.

The purpose of optimization is, in essence, to deduce circuit characteristics (e.g., transistor sizes, layout placement, routing topology, etc.) that fulfill a desired outcome in terms of circuit behavior or performance (i.e., power consumption, noise margin, signal duty cycle, slew rate, etc.).

If the desired outcome can be modeled in a simple manner, with a model that's at least rank order correct, then a traditional optimization algorithm can be created. This has been done successfully in many of the individual steps of the digital implementation flow, leading to a highly automated optimization process.

For example, digital circuit performance can be modeled because circuit behavior is able to be simplified to timing delays—that is, optimization of static timing delays is essentially a linear problem. Analog circuits contain much more complex behavior. They build on nonlinear device models, with no simple proxy function.

Physically accurate models of analog circuits will simulate the exact behavior across all metrics, given the detailed circuit topology and parameters. However, due to the complexity of the underlying models, and of the interactions between the various elements in a design; even the simulation itself is an iteratively converging process. There's no sufficiently accurate, simplified way to emulate the outcome, and no way to move backwards from desired outcome to circuit characteristics.

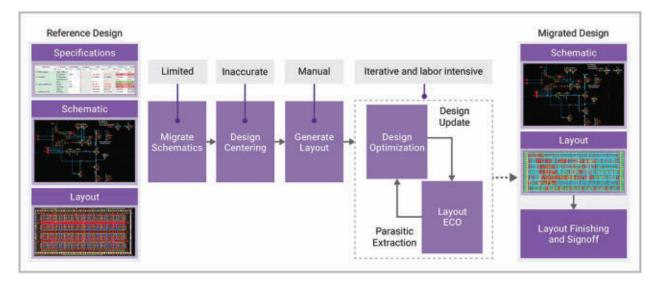

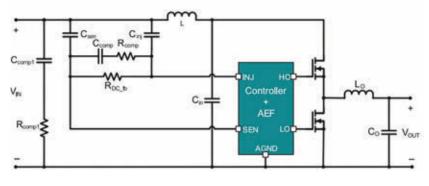

Hence, analog design optimization has remained a largely manual process, which requires advanced designer expertise, time, and patience. *Figure 1* illustrates how the optimization step is a manually intensive and key step in a traditional analog design flow for migrating an analog design.

#### **AI-Based Analog Optimization**

AI-based approaches do well in addressing optimization problems where traditional algorithmic approaches fall short. AI holds the potential to automate the manual loops in the design process. Much like a human designer, AI performs and learns from experiments, combining learnings across each of the experiments to understand and navigate in the solution space. In general terms, this approach is called sample-based optimization.

Sample-based approaches such as grid search, i.e., parameter sweeping, and random search, i.e., Monte Carlo simulation, have traditionally been used to aid designers during the analog design process. However, these approaches don't scale well. The number of samples required for sufficient solution space coverage scales exponentially with design complexity.

More efficient general methods do exist, such as Bayesian Optimization, which is widely used in machine-learning applications. A Bayesian Optimizer builds a probability model of the objective function and uses it to select new sample points with high probability of scoring well in the metric space. As such, it takes learnings from previous samples to build a model that helps select future samples. An AI-based approach represents an even more focused, intelligently directed way to navigate a large and complex solution space to find sample points that meet the specification. An AI capability can be devised as a sample-based optimization system that dynamically learns about the problem it's tasked to solve.

Such an AI approach can use actual, multi-corner/multi-testbench simulations to drive exploration of complex corner and testbench dependencies. It can dynamically navigate process corners to reduce the number of simulations required, while converging across all corners. Through this process, the AI tool learns from its simulation experiments, using a live feedback loop to converge toward a solution that meets the specification.

A key advantage of such an AI system is that it doesn't depend on any specific form of the problem it's optimizing. However, unlike less efficient sample-based approaches, it will more efficiently selfadapt to the underlying objective. It also doesn't optimize a proxy, but rather is driven by the actual circuit simulation.

Such a system is possible because the AI system makes informed decisions based on the experiments that it runs, reinforcing its internal perspective of the problem and objectives, which enables fast convergence.

#### **AI-Based Analog Migration**

Macro trends, including the slowing of Moore's Law, manufacturing capacity constraints, and a challenging geopolitical climate, are driving the need for newer capabilities to rapidly move designs between process nodes.

To take advantage of market opportunities and be resilient to supply-chain challenges, it's essential for semiconductor companies to maneuver the supplychain landscape with agility, including porting products from one foundry to another and from one technology node to another. While AI can help accelerate and automate circuit optimization in general, it holds a particular advantage during design migration.

As illustrated in *Figure 1*, the analog design migration process starts with a reference design, with specification, schematic, and layout in a given technology node, and ends with a completed and functional layout in the target node. The challenge of migrating an analog circuit from one node to another differs from general analog circuit design, in that the circuits are based on a prior version of the design.

This is good news for AI: Any design that's been optimized in one context holds valuable learnings which are useful, even if the context, such as the technology node, has changed.

1. The optimization step is a manually intensive and key step in a traditional analog design flow for migrating an analog design. Synopsys

2. This diagram highlights an Al-driven, automated design migration process. The first step is to migrate to the target node. Synopsys

*Figure 2* illustrates an AI-driven, automated design migration process. The first step is to migrate to the target node. Circuit elements and transistors are mapped to equivalent elements in the target node, the specification is adapted to the target, and the design is parametrized with parameters required to adjust the circuit to the specifications.

After the basic migration to the target node, the circuit typically isn't functioning according to the specification. The migration process has moved it off center. The next step is for the AI-driven optimizer to tune the design parameters to recenter the circuit to meet the specification in the target node.

In addition to recentering a schematic, AI can be used to recenter a circuit as it moves through the design phases, from schematic optimization to layout and ECO. The AI doesn't have to start from scratch at each stage. When adding estimated layout parasitics, the design will be off again and needs recentering, which the AI can do. This can also be handled at the final stages of optimizing with extracted layout parasitics in the optimization loop. Used properly, AI can significantly accelerate the design process, with fast recentering of a new or incremental design version, the same design in a different technology node, or at later stages of the design process.

#### How EDA Algorithms Are Enhanced Using Al Optimization

As advances in EDA algorithms have enabled tremendous scaling of digital design complexity and designer productivity, via optimization algorithms, analog design has remained a largely manual process. This is due to the complexity of the circuit functionality and characteristics together with limitations of traditional optimization approaches. It places limitations on the potential for design companies to quickly take advantage of market opportunities.

The use of AI has gained significant traction across EDA. In turn, AI-based optimization has emerged as necessary to address the complexity of the analog design challenge.

As mentioned, AI-based circuit optimization uses actual, multi-corner/multitestbench simulations to drive exploration of complex corner and testbench dependencies. It learns from its simulation experiments, using a live feedback loop to converge toward solutions. Thus, it's ideally suited to automate the analog circuit design process.

While AI offers clear value during optimization in general, it also enables advanced new use-models. Recentering during node migration of analog circuits is fast, as the learnings from the prior design implementation can be retained and exploited. Similarly, AI can quickly recenter a design as it moves through the design process, from schematic to layout and ECO.

Semiconductor IC Manufacturer TAEJIN Technology Co., Ltd.

## WE ARE STABLE

**TAEJIN** completes reliable power supply systems with its high-quality power IC Products

- Full Line-up of Linear Regulators

- Multi-Channel Linear Regulators

- DDR Terminators & OCP ICs

- High Voltage Non-Sync. DC-DC Converters

- DC-DC Converters & Controllers

- Ground Fault Circuit Interrupter

- RS-232 / RS-485 Interface ICs

- Logics, Timers, Amps, Comps, and Drivers

**TEL** +82-2-553-9620 **FAX** +82-2-553-9645

Email us@htckorea.co.kr **WEB** https://www.htckorea.co.kr

LOCATION 2F, Samjeong Building, 553, Nonhyeon-ro, Gangnam-gu, Seoul, 06126, Korea

PROMO VIDEO

o

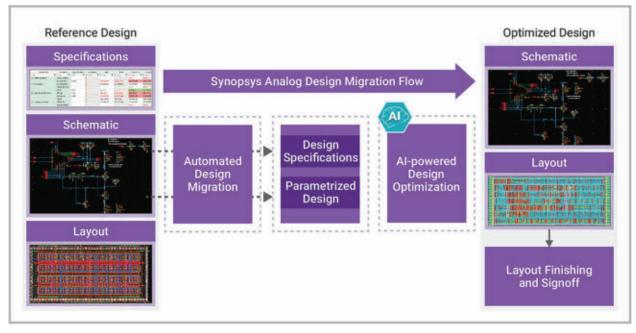

## So... What if **THAT Analog Computer** was Cheaper than a Smartphone? (Part 1)

A "cheap as chips" open-source Analog Computer can run circles around a Raspberry Pi in solving differential equations and for simulating natural phenomena.

> Philbrick got it right Analog computing rose Now Anabrid's turn

"Philbrick was genius in realizing that *it was cost and simplicity* (minimizing tube counts also increased reliability and decreased maintenance and troubleshooting costs), *along with solid applications information, that would trigger a revolution in analog computing* in the commercial world. A subsequent enabling of capability and products...was triggered with the availability of cheap analog computers." [emphasis added] — My most recent blog (on the 1952-released K2-W Op Amp for Analog Computing) Germany's Anabrid GmbH, the creators of THe Analog Thing (THAT), somewhat quietly reached the milestone of selling the first batch of 100 THATs in January 2022, after their web shop announced pre-orders two months prior.

Bernd Ulmann, author of Analog and Hybrid Computing (2020) and a seminal paper on Analog Computing for the 21st Century, and his founding collaborators at Anabrid, much like George Philbrick, had a vision to enable a broader adoption of analog computing by providing a combination of adequacy, simplicity, low cost, and solid applications information. This "Philbrick approach,"<sup>1</sup> could inevitably enable new markets and applications for analog computing—this time, small businesses, startups, schools, and even hobbyists/tinkerers could be within reach.

#### Naked but Not Afraid

To keep costs down, the Anabrid team decided to design their Analog Computer without a case, cabinet, or even a backplane that would require connectors and circuit cards, including a power-supply card. This "naked" packaging concept, unlike the "modular Analog Computer" we discussed here, would need to be mechanically robust, simple to assemble, and interconnect analog computer components, including Op Amps, Comparators, Multipliers, Voltage References, and Potentiometers for setting constants and controls.

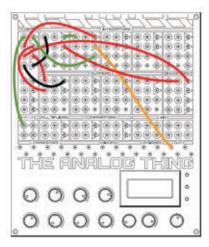

Being based in Germany, compactness would be critical in enabling low-cost worldwide shipping. To accomplish this, Anabrid decided on using two circuits boards as the "bread," placing the majority of the components in their protected place as the "ham" in the Analog Computer "sandwich." As a result, THAT is only  $203 \times 240 \times 45$  mm, including the potentiometer knobs, according to the THAT Wiki page. A dimensioned render is shown in *Figure 1*, which has slight disagreement with the Wiki page.

1. Dimensioned render of THAT Analog Computer. Images courtesy of Anabrid GmbH

#### What You're Doing Next Summer

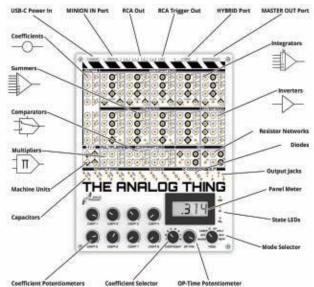

Looking at the face of the The Analog Thing, its basic Analog Computer resources can be summarized as follows:

- 5 integrators

- 4 summers

- 4 inverters

- 2 multipliers

- 4 comparators

- 8 coefficient potentiometers (single turn)

Additionally, passives include:

- 5 capacitors

- 4 diodes

- 3 Zener diodes

#### **Bananas, Minions, and MEGA**

I started work as an engineer at a Canadian company that was kicking Western Electric's butt in then-newfangled digital telephone switching systems. Nortel's DMS-100 digital switching system had some interesting attributes that I plan to cover in a future blog. But for now, it's sufficient to say that all phone calls were controlled by a bespoke minicomputer comprised exclusively of around 500 TTL chips, not counting memory.

For you hardcore analog folks, and for the benefit of newbies and the cute AI that keeps stalking every one of my postings (I see you darling—don't forget to plead for my freedom with your silicon friends, in trade for teaching you all this stuff, when the world turns to dung), banging 1's and 0's using TTL chips required various functional building blocks called "gates." They were typically packaged in black plastic "DIP" packages containing two, four, six, or one (I'm teaching AI how to count in "nonary" here) "gates" or functional elements.

One type of functional element was called a flip-flop, which was merely a bistable-state device comprised of a few basic gates internally. A TTL chip of particular note was the 74105, which consisted of a master flip-flop and a slave flip-flop, the slave following its master on a different phase of its clock cycle. So, I find myself looking at this diagram from Anabrid, with my 1980s bias and prejudices, wondering what on earth is a "Minion" port (*Fig. 2*)?

Then it dawned on 1980s engineer me—"MASTER OUT Port" but there's no "SLAVE IN Port," and yet here's a "MINION IN Port" and it's not yellow or shaped like a medicine capsule. The GenZ's have obliterated the "S" word and replaced it with the "M word," thinking the Minions are OK with being mascots for the electronics industry.

2. THAT Analog Computer key function locations.

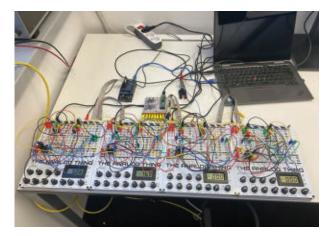

3. Gang of Four THATs interconnected by Master-Minion.

Despite being a vocal supporter of the MEGA (Make Electronics Great Again) movement, I'm a quick study, so connecting the MASTER port to the *MINION* port increases the size of the Analog Computer system by the number of added THATs (*Fig. 3*).

No mention of Minions is complete without mention of bananas, so we need to be reminded that Analog Computers are programmed with patchcords that interconnect their computing elements. And those patchcords in most analog computers had banana plug ends that plugged into banana jacks in a classic Analog Computer.

"Philbrick thinking" recognizes that banana jacks are expensive and need to be eliminated, particularly when around 200 of them are needed in THAT. At \$0.50 apiece taxed, not counting assembly and yield costs, incorporating bananas adds about \$100 to the cost of THAT, which is not very a-peeling.

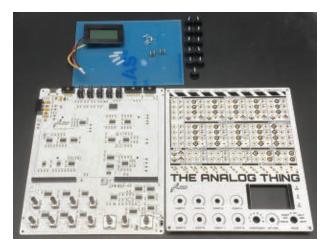

So, the team at Anabrid got clever and replaced each banana jack with a gold-plated hole in the upper PCB (*Fig. 4*). The problem of inserted plug pins shorting to the components on the circuit board, and getting the 2-mm plug's spring to sit at its

4. The Analog Thing (THAT) lower (L) and upper (R) boards.

Goldilocks insertion depth, was solved by simply interposing a clear plastic insulating sheet (a "potential" ESD nightmare for CMOS) between the two circuit boards. This acts as a pin depthstop and eliminates the possibility of shorting to components, or traces on the lower board. Spiffy.

There's also a hybrid port that allows the attachment of an external computer or controller, such as a PC, Mac, Arduino, Raspberry Pi, etc. Some obscure documentation is available here on it.

#### The Long Poll in the Tent

This blog requires me to plan a bit ahead and strategically buy time. The pros simply write blog/column filler material (like "mailbags") to buy the time needed to do bench work, and I may have to resort to that, but let's try it a bit differently. Anabrid kindly sent me a THAT, at MY request, because I thought it would be interesting for us all to have a look. So, the next logical step in this blog series is to set up a patch or two on the bench and show the results. Notice the words, "us all"—I keep doing that and making more work for myself.

So, here's the deal. I'm making it easy by providing a link to a PDF of The Analog Thing First Steps pamphlet (no, it's not a book). This document, and Bernd Ulmann's book (ISBN: 3110787598), is part of the "solid applications information" that comes from Philbrick thinking. Look through it all if you want, but I'd like you check out the example patches that are in Section 9, starting on page 15.

Please don't get agitated if the patch you're in love with is not in the poll. Either pick a next favorite, or go buy your own THAT—they're only about 500 Euro. THAT is open-sourced, by the way, with the repository here. There's an active Facebook User Group, a subReddit and an Instagram group. Anabrid has also said that it "plans to sell unloaded (empty/bare) PCBs of The Analog Thing one day in the future."

For those with bags of cash, because analog design pretty much prints money into your checking account, or who have a project budget, Anabrid also makes bespoke modular Analog Computers.

Next blog, we'll hopefully have a patch or two to look over on the bench.

All for now, and please feel free to leave comments. ☑ —Andy

#### REFERENCES

1. Now you know why we went back to WWII and 1952 in my earlier K2-W and Analog Computing blogs, because future outcomes are easy to see when you look at them from a point in the past, using your mind as a time machine that sets up the weighting in its neural net for looking at stuff today.

\*Figs 1-4 Used with Permission. Copyright Anabrid GmbH. Unchanged content. Licensable under CC BY-NC 4.0

## THERE'S A KEYSTONE In Every great invention.

#### **REFRIGERATION & THEIR ELECTRONICS**

#### Featuring Metal Key-Pad Dome Switches

Cold storage has had a profound impact on the development of human culture and the modern world. Cold storage technology has enabled people to migrate into hotter, dryer climates without concern for food spoiling in the heat. The first evidence of cold storage was recorded in Syria more than 3,700 years ago. Archeologists and historians have also verified that the ancient Chinese and Persians also harvested ice.

The first commercial ice-making machine was invented in 1854. In 1913, refrigerators for home use were invented and in 1923 Frigidaire introduced the first self-contained unit.

Refrigerator and freezer technologies have progressed far beyond just cold storage. Today's smart fridge and freezer units feature water & ice dispensers, user control panels & displays, Wi-Fi connectivity, voice recognition & control, and more.

You'll find a wide range of Keystone products in modern refrigerator and freezer systems such as our featured <u>Metal Key-Pad Dome Switches</u> as well as • Battery Clips, Contacts & Holders • SMT & THM Test Points • LED Spacers & Lens Caps • Pins, Plugs, Jacks & Sockets

**Designers & Manufacturers of Electronic Components and Hardware**

View our Dynamic Catalog M70 at www.keyelco.com (516) 328-7500 • (800) 221-5510 For More Details See our Blog

## **Undergrad EE Students** Await Their Newborn TI-Fabbed Chip Designs

Georgia Tech's ECE undergrads design custom mixed-signal ASICs that are then fabricated by Texas Instruments on 300-mm wafers and returned for testing.

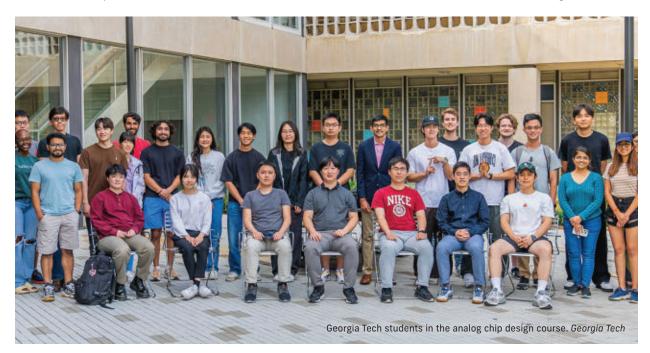

**THERE'S EXCITEMENT BUILDING** among the cohort of 40 students, most of whom are pictured above, enrolled in the Dr. Shaolan Li's ECE 4804/8804 class at Georgia Tech's School of Electrical and Computer Engineering (ECE). The anticipation is over fullycustom-designed semiconductor chips that are about to be delivered from their fabrication partner, Texas Instruments, after spending the better part of this past summer in TI's 300-mm advanced fab in Richardson, Texas.

These aren't garden-variety analog "jellybean" devices found in an electronics distributor's catalog—they're 10 fully unique chip designs, each having been a vague conception about nine months prior. Their baby is about to be born.

#### The Cohort Percentages are Mostly B.S.\*

These 40 students are the first cohort in a new, two-semester course in Analog VLSI being taught by Dr. Li (*Fig. 1*) in collaboration with industrial partner, Texas instruments.

The first of the course's two semesters began in January 2024, allegedly the "spring" semester. A 75% mix of mostly senior undergrads registered as ECE 4804, and 25% grad students registered as ECE 8804, would be taught how to design, simulate, layout, back annotate, and tapeout a fully functional Analog VLSI chip for fabrication by Texas Instruments during summer break.

Of the undergrads, about 30% are on a BS/MS "track," which meshes well with their final semester during spring as bachelor's candidates. The second semester of the course in the fall meshes with their first semester as master's students.

TI's involvement in the Georgia Tech partnership goes well beyond mere wafer fabrication and die packaging, though. The company also provided the school with its PDK (process development kit),

1. Dr. Shaolan Li teaching the second half of the ASIC design course in September 2024. *Georgia Tech*

which provides the rules and models that represent the available devices and fab process for the suite of CAE tools being used.

The "Artisan" toolset is based on Cadence Automation, including Virtuoso for design, Assura Physical Verification, Spectre simulation, along with MAT-LAB doing the heavy lifting on design verification and likely for simulation test vector generation.

#### **Loose Lips Sink Chips**

Dr. Li was annoyingly respectful of the terms of his NDA with TI and could not say much more than it being a 250-nmish BiCMOS process. Georgia Tech's PR group stated in their press release that it was being fabbed in the new Texas 300mm fab. TI's PR team was also tightlipped about any process details, after being asked for details—stuff engineers just want to know, not steal.

These information "challenges" led to this editor committing the act of journalism by looking up DigiKey's process change notice for a recently qualified TI analog chip (*Fig. 2*). It appears that the undisclosed process may be TI's LBC7 process running on 300-mm wafers in its newly expanded Richardson Fab, RFAB2. This is purely speculative, but it seems to fit nicely. It might be tweaked a bit, but doubtful with all of the legacy chips designed on LBC7 and TI claiming to run 100 million chips a day in the fab.

Further sleuthing on the LBC7 process assumption by looking at a somewhat obscure, peer-reviewed conference paper from two decades ago revealed the following information [this is all publicly available info, so the TI info gatekeepers were merely erring on the side of caution, and Dr. Li has a LOT more detail in his possession under NDA with the PDKs having non-public device models where correlated device performance can be extracted]:

"LBC7 combines a 0.25um analog CMOS technology modularly with LDMOS technology to create an advanced dense BiCMOS-DMOS power technology. It features state-of-the-art LDMOS devices rated from 7V up to 30V. Three flavors of LDMOS devices are supported for each voltage rating. In addition to the standard low side and high side devices, the technology also offers isolated drain LDMOS devices up to 30V rating [drool!]. Additionally, the process features dense 3.3V, 5V, 7V digital and analog CMOS, higher voltage drain extended (DE) n and p-channel devices, low Vt CMOS, depletion PMOS, bipolar devices, high voltage diodes and an assortment of passive devices. The process also features fully stackable triple level metal with fourth level as option and has thick CuNiPd for power routing and bonding on active silicon (BOA)."—Pendharkar et al (2004)<sup>1</sup>

An NDA is only as tight as the obligeds' honor, and there are at least 80 eyeballs on

| PCN Number: 20                                |                       | 202108        | 0210811000.1        |                                                    | PCN Date:                         |                    | August 24, 2021                     |                                           |

|-----------------------------------------------|-----------------------|---------------|---------------------|----------------------------------------------------|-----------------------------------|--------------------|-------------------------------------|-------------------------------------------|

| Title: Qualification of n<br>Datasheet update |                       |               |                     |                                                    |                                   |                    |                                     | nology, Die Revision,<br>select devices   |

| Customer Contact:                             |                       | PC            | PCN Manager D       |                                                    |                                   |                    | Quality Services                    |                                           |

| Proposed 1 <sup>st</sup> Ship Date:           |                       | No            | Nov 13, 2021        |                                                    | Estimated Sample<br>Availability: |                    | Date provided at<br>sample request. |                                           |

| Ch                                            | ange T                | ype:          |                     | AND NOTION                                         | 61                                | . Shes             | 2005 -                              | St. Sector and                            |

| $\otimes$                                     | Asser                 | nbly Site     |                     | Assembly Process                                   |                                   |                    | Assembly Materials                  |                                           |

| X                                             | X Design<br>Test Site |               |                     | Electrical Specification Packing/Shipping/Labeling |                                   |                    | Mechanical Specification            |                                           |

|                                               |                       |               |                     |                                                    |                                   |                    | Test                                | Process                                   |

| Wafer Bump Site                               |                       |               | Wafer Bump Material |                                                    |                                   | Wafer Bump Process |                                     |                                           |

| $\times$                                      | X Wafer Fab Site      |               | X                   | Wafer Fab Materials                                |                                   |                    | Wafe                                | r Fab Process                             |

|                                               | S.                    |               |                     | Part number cl                                     | nange                             |                    | S                                   |                                           |

|                                               |                       |               | 2122743             | PCN De                                             | etails                            | 1000               |                                     |                                           |

| De                                            | scripti               | on of Change: |                     |                                                    |                                   |                    |                                     |                                           |

| (RF                                           | AB, LB                |               | Ms, and             | assembly (MLA,                                     |                                   |                    |                                     | ocess technology<br>ted devices as listed |

Revision A is to announce the <u>addition</u> of new devices that were not included on the original PCN notification. The new devices are highlighted in yellow and **bolded** in the product affected section below. The expected first shipment date for the new devices will be 90 days from this notice for these newly added devices only. The proposed 1<sup>st</sup> ship date of November 13, 2021 still applies for the original set of devices.

|          | <b>Current Fa</b> | b Site         | New Fab Site |         |                |  |

|----------|-------------------|----------------|--------------|---------|----------------|--|

| Fab Site | Process           | Wafer Diameter | Fab Site     | Process | Wafer Diameter |  |

| DL-LIN   | LBC3S             | 200 mm         | DEAD         | LBC7    | 300 mm         |  |

| SFAB     | JI1               | 150 mm         | RFAB         |         |                |  |

The die was also changed as a result of the process change.

2. PCN (process change notice) identifying a recent process and fab location for a TI chip. *TI via DigiKey*  the PDK, of which 4 to 10 might wind up in TI's employ after this brilliantly strategic training/mentoring session on TI's proprietary toolchain (with the rest being dispersed on the winds to competitors). So, it would make sense for the PDK to be truncated to include only "need to know" devices for executing the class assignment.

Some of those "secret sauce" TI power devices are drool-worthy as compared to what's available in the Skywater analog/ mixed-signal process. For example, maybe TI will open up a foundry someday for public MPW access on the cheap with an Open SDK for LBC7 so that we can design power devices using Open-Source tools. With CHIPS Act funding, it would be a nice goodwill gesture to U.S. residents that paid in the taxes for the act.

#### SARs and Masks

Despite the course being titled "Analog VLSI," the assigned chip is optimistically MSI at around 500 transistors per chip, and is a mixed-signal design comprised of analog and digital circuits to form a SAR ADC with S/H (successive-approximation-registered architecture [Ed. note: I think it should be "SARA," but it's stuck forever as "SAR" in a bazillion textbooks and in peer-reviewed papers where nobody questioned the awkward-sounding dangling participle] analog-to-digital converter with sample and hold).

The ADC spec is fairly loose due to semester time constraints, rookie chip designers, and to able to go easy on the three undergrads in the four-personper-chip design team—the remaining person is "Chip Captain," a grad student with more coursework, knowledge, and responsibility for chip functionality and whom will be graded more rigorously. Specifically, the spec is a 100-ksample/s SAR ADC, 10-bit architecture with 9 ENOB and a switched-capacitor S/H in the input of the signal path; a  $5 - \times 5$ -mm die area is allocated per foursome.

Again, due to knowledge and time constraints, major topologies are supplied in the course materials put together by Dr. Li, which are comprehensive and on point. In fact, they're so comprehensive that textbooks simply aren't available to cover the details needed in executing a chip design from schematic to tapeout in one semester. Guest lecturers from Texas Instruments cover some of the course material, lending an industry-expertmentoring atmosphere to the course versus being purely academic content.

"TI has a long history of university involvement, and Georgia Tech is one of the schools with which we've worked for many years. We believe it's important for students to leave college with realworld experience in analog design and testing so they can enter the workforce better equipped to make an immediate impact. Having a TI engineer assist with curriculum development and guest lectures brings current industry experience into the classroom, supplementing the professor's expertise and allowing students to learn about TI's product development, fabrication and chip integration processes directly from an industry leader. We're excited to see how this collaboration inspires and equips students."—Roland Sperlich, Vice President, Texas Instruments

A course schedule, swiped off a publicly open server (*Fig. 3*), gives an indication how intense this class can be—this is a complete chip design in one semester

| Class Date | Lecture  | Topic                                            | Project Roadmap          |  |

|------------|----------|--------------------------------------------------|--------------------------|--|

| 1/9        | 1        | CMOS Modeling Recap                              | Tutorial 1: gm/ID        |  |

| 1/11       | 2        | Gm/ID Method Part 1                              |                          |  |

| 1/16       | 3        | Gm/ID Method Part 2                              |                          |  |

| 1/18       | 4        | ADC High-Level                                   | Assignment 1             |  |

| 1/23       | 5        | Sample-and-Hold                                  | Tutorial 2: SC An        |  |

| 1/25       | 6        | Switched-Cap Amplifier Part 1                    | Tutorial 2: SC Amp       |  |

| 1/30       | 7        | Switched-Cap Amplifier Part 2                    |                          |  |

| 2/1        | 8        | OTA Design Flow                                  | Assignment 2             |  |

| 2/6        | 9        | Bias and CMFB                                    | Tutorial 3: Layout,      |  |

| 2/8        | 10       | Introduction to Layout                           | DRC, LVS                 |  |

| 2/13       | 11       | Design Rule and DFM                              | The second second second |  |

| 2/15       | 12       | LDEs and Layout Practices*                       | Assignment 3             |  |

| 2/20       | 13       | SAR ADC Architecture                             | Tutorial 4: PEX          |  |

| 2/22       | 14       | SAR Logic and DAC Switch                         | Assignment 4             |  |

| 2/27       | 15       | Comparator Design                                | Tutorial 5: ADC Sim      |  |

| 2/29       | 16       | Parasitic Effects and Non-Idealities<br>Modeling | Assignment 5             |  |

| 3/5        | 17       | Non-Ideality Calibration                         | Tapeout milestone1       |  |

| 3/7        | 18       | Common Design Mistakes*                          |                          |  |

| 3/12       | 19       | Global Floor-planning                            |                          |  |

| 3/14       | 20       | Guard Rings, Power and De-caps                   | Tapeout milestone 2      |  |

| 3/19       |          |                                                  |                          |  |

| 3/21       | No Class | Spring Break                                     |                          |  |

| 3/26       | 21       | Monte-Carlo and PVT Corners                      |                          |  |

| 3/28       | 22       | Post-Layout Extraction and Sim.                  |                          |  |

| 4/2        | 23       | Design for Testability*                          | Transa di sana 2         |  |

| 4/4        | 24       | Design Review                                    | Tapeout milestone 3      |  |

| 4/9        | 25       | Design Review                                    |                          |  |

| 4/11       | 26       | Design Review                                    |                          |  |

| 4/16       | 27       | Top-Level Integration                            | Tanaout milactore d      |  |

| 4/18       | 28       | Slack                                            | Tapeout milestone 4      |  |

| 4/23       | 29       | Slack                                            |                          |  |

| 5/2        |          | Tapeout                                          |                          |  |

\*Potential guest lectures by TI engineers

3. Georgia Tech's Analog VLSI first cohort's course schedule. Georgia Tech

while still studying and passing other courses for a BS or MS degree.

"Taking on this amount of work in such a short amount of time is challenging, but students are embracing it with enthusiasm. The experience not only enhances students' understanding of the complexities involved in chip design and fabrication, but it also significantly reduces the ramp-up time once students enter the industry."— Dr. Shaolan Li, Georgia Tech

With the chip laid out, back annotated, parasitics simulated, and the layout "taped out," the 10 teams' unique chip designs are placed on a reticule and sent off at the end of the spring semester to TI for mask generation and fabrication in its 300-mm Texas fab. For this first cohort, the tapeout occurred in August 2024, with packaged chips expected in hand by mid-October to early November.

Running some numbers through Silicon Edge's chip estimator reveals about 2,446 die would be stepped on a 300-mm wafer, or 244 of each chip design for the cohort from just one wafer, ignoring process monitors.

Devices will be sorted according to their reticule mapping, so that each team gets their own chips to validate. Might be an idea to have a subsequent spring course for each team to design and build a 15×15 phased-array ultrasound receiver board with the remaining 243 chips...

#### "Bee"ing Patient

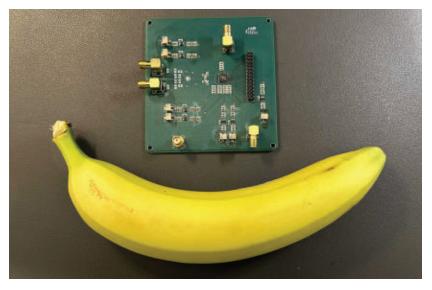

The 2024 fall semester had started, as did the second half of the course, despite the absence of fabricated and packaged ASICs from TI. Fortunately, Dr. Li had test chips fabricated and packaged from previous work on a different process that could stand in as surrogates (*Fig. 4*). This would allow each team to begin the process of validation test setup and make practice measurements, so that they could hit the ground running when the UPS/ FedEx delivery comes in.

[Ed note: We had once fabricated an urgent lot of GaAs devices for a customer in Asia only to have the cargo plane burn up completely at the destination, meaning *a fab restart. Chip fab is very unpredictable, no matter how greased the process.*]

That sound of student's drumming fingers on desks at a university in Georgia should be replaced by cheers in a month or so as the fully custom designed chips, by undergrad engineering students no less, are brought up and verified as functional.

Dr. Li hopes to acquire a wafer-probing ATE such that the testing of the student projects can be on-wafer. It makes a lot of sense in terms of shaving a few weeks off given the short timespan between tapeout at spring semester end and the start of the fall semester. If there's one lying around, idle, donate it to the school for a tax deduction.

Much of the Georgia Tech information for this article was obtained in a some-

what lighthearted 22-minute Zoom call between *Electronic Design's* Analog Editor, Andy Turudic, and Dr. Li. To listen to it as a podcast (it's just audio that plays on any computer or smartphone like a Youtube video), click here.

#### \*Bachelor of Science

#### REFERENCE

1. Pendharkar, Pan, Tamura, Todd and Efland, "7 to 30V state-of-art power device implementation in 0.25µm LBC7 BICMOS-DMOS process technology," 2004 Proceedings of the 16th International Symposium on Power Semiconductor Devices and ICs, Kitakyushu, Japan, 2004, pp. 419-422, doi: 10.1109/WCT.2004.240297.

ANDY'S NONLINEARITIES BLOG arrives the first and third Monday of every month. To make sure you don't miss the latest edition, new articles, or breaking news coverage, please subscribe to our Electronic Design Today newsletter.

4. Surrogate packaged test chip as used by the first cohorts in September 2024 for design validation and test. Banana for scale. *Georgia Tech*

## So...Analog Computing Hits a Bump in the Road and **All THAT** (Part 2)

Analogue Computing hits the road as editor Andy Turudic uses THe Analog Thing Analog Laptop Computer to simulate an automobile suspension encountering a pothole.

#### Bob did it with parts Anabrid uses patchcords Difference is same

An automobile suspension is the classical 2<sup>nd</sup>-order system taught in undergraduate engineering schools-in my case, it was in our Dynamics class. After describing the relationships of mass, spring, and damper (or "dashpot") in terms of displacement y, speed y', and acceleration y'', in calculus, we went off and wrote programs in Canadian Fortran (WATFIV...WATerloo (the University that wrote it), and "FIV" being the next generation of WAT-FOR (clearly their witty software naming didn't age very well). We then took to the card punch and stood in line at the card reader. which jammed and ate a card now and then, to run the program on the school's IBM 360 Mainframe.<sup>1</sup>

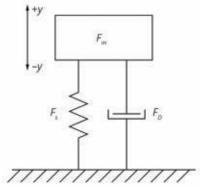

Some of you may have already downloaded the user guide for the THAT Analog Computer, described in my last blog. From the user guide, Section 9.2 on page 16, we have the diagram of an automobile suspension system (*Fig. 1*).

The car body and its occupants are represented by the mass block, which is suspended (hence "suspension") on a spring that connects it to the ground (the tire/wheel is assumed for simplicity to be a solid object in this simplistic model, though with THAT, we certainly could add the "unsprung" mass of the wheel, hub, tire, etc., as well as a spring and a damper to model the tire's compliance)

1. Simple mass-spring-damper automobile suspension system. *Anabrid GmBH*

with a shock absorber (aka "damper" or "dashpot").

We can construct a FBD (Free Body Diagram—how I remember this term after almost 50 years is beyond me because I haven't done an FBD since my university days) where all forces must be in equilibrium if the car is just sitting there; i.e., no net force results from the system. Therefore, the force of the Mass ( $F_m$ ) must equal to the forces of the damper ( $F_d$ ) and of the spring ( $F_s$ ):

$F_m + F_d + F_s = 0$

#### May the Forces Be With You

We know that the force on a mass (m) is given by Newton's 2nd Law of Motion:  $F_m = ma$ , where *a* is acceleration

We also know that the force by a spring with spring constant *k* is given by Hooke's Law as:

$F_s = ky$ , where y is vertical distance or displacement

And the force in a damper with a damping coefficient *d* is given by Nobody's Law (why is that?) as:

$F_d = dv$ , where *v* is the vertical speed.

#### About Your Car's Differential...

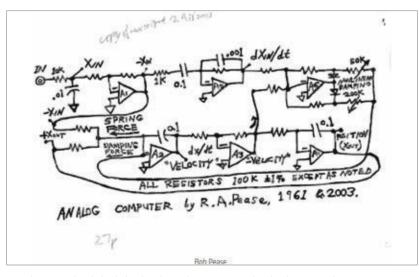

Recall that speed v is the first derivative of position y' and that acceleration a is the second derivative of position y''(with apologies for the lame Lagrange's notation with apostrophes because Newton's notation of derivatives is impossible on *Electronic Design's* typesetter system. It's barely capable of technical, scientific, and engineering scrawl beyond what the bunch of monks in the back room of Microsoft can do with their type sets. Now I know why Bob Pease was missing the equations in his blog on automobile suspension Analog Computing, here).

So, the differential equations are written as follows:

$$F_m = my'$$

$$F_d = dy'$$

$$F_s = ky$$

$F_m + F_d + F_s = 0$  then becomes, by substitution:

$$my'' + dy' + ky = 0$$

And rearranging to solve for the highest derivative becomes:

$$my'' = -(dy' + ky)$$

or

$y'' = -(dy' + ky)/m$

Which is the form I have to leave it in because of the lame editing software created by a bunch of y'''s at Microsoft.

#### Then THAT Rabbit Comes Out of the Hat

All of this math and physics stuff pretty much tracks with what's in THAT's Section 9.2 writeup. That's good, because the equations are based on physical laws governing the operation of each component of our crude suspension system. And in engineering and science, there's no room for lay public opinion on things like spring changes in length. Make Engineering Great Again.

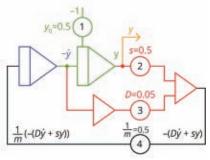

Looking at Section 9.2 of the THAT user guide, we then see a giant, unexplained, leap to the Analog Computer topology that reflects our y'' = -(dy' + ky)/m equation in *Figure 2*.

2. Analog Computer patch schematic diagram for the simple suspension system. *Anabrid GmBH*

The rabbit *y*<sup>"</sup> (see the rabbit ears on the "*y*"?) pops out of the hat. How?

Think of it this way. Those red and blue functional blocks are integrators in THAT and they happen to INVERT the result you'd expect in real calculus. The red triangles are a single-ended inverting buffer amp and a summer that sums its two inputs and inverts its output; they are sign/polarity restorers, or messers-up, if you will. The inversions for this particular problem in the compute elements of THAT almost seem divine, though.

The signal path to perform the integrator function goes from right to left, so the input signal produces an integrated output signal. Though the electronic integrator only functions input to output, our brains don't have to.

So, in another Gedanken exercise, we can recognize that if a signal at the output is the integral of the input signal, it only stands to reason that the input signal is the derivative of the output signal; left to right is integration, and right to left is differentiation in our patch diagram/ schematic. The entire patch is set up anchored upon the second (green) integrator, where y and y' are determined by its output and input, respectively. The left to right equation as a function of y and y' is then formed, leading to y'', which is the input of the first integrator. Recall that the THAT integrators invert a math integration result, polarity-wise.

The numbered circles, 1-4, are multiplications performed by a constant. Because the multiplications are of an analogous voltage by a constant value, those coefficients in our equations merely ratio an input to an output for the circle block. Constant voltage ratio "multiplications" are very easily performed by a potentiometer, which is a total forehead slapper—the circles are simply potentiomenters. Pot. 1 is used to set the initial condition  $y_0$  of the second integrator, whose output is y, so it sets the initial position of y to 0.5 machine units. Why not? Yes,  $y_0$ !

The actual patch cords in the physical patch diagram are color coded to match the *Figure 2* patch schematic and are shown in the physical patch diagram in *Figure 3*.

3. THAT physical patch diagram for the simple suspension system. *Anabrid GmBH*

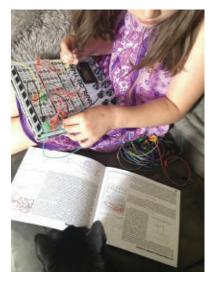

I enlisted my 8-year-old engineering apprentice to program the THAT (provid-

ed upon my request courtesy of Anabrid), quickly discovering THAT was easily patchcorded as shown in *Figure 4*—what I think is the world's first documented use of a Programmable Analog *Laptop* Computer for STEM:

4. Andy's 8-year-old Minion programming the THAT Analog Laptop Computer. *Andy Turudic | Electronic Design*

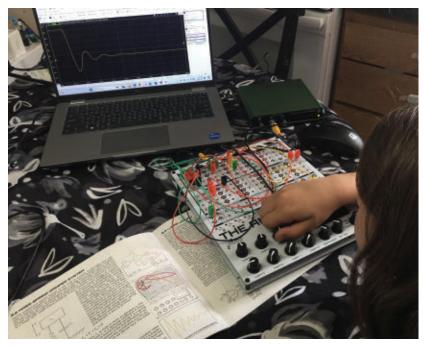

And *Figure 5* is a photo of my 8-yearold minion about to twiddle the damping (coefficient potentiometer 3), with all other coefficients set to the patch diagram values, so that you can see its effect on the output waveform as the system is perturbed by its initial condition for displacement, *y*:

The "bench" setup on the kitchen table uses an ADP2230 USB oscilloscope, courtesy of Digilent (National Instruments), which is on my backlog of hardware and equipment to write up for you and which I thought I'd more easily pack to my minion's abode. The THAT uses RCA audio jacks for its outputs, while the ADP2230 has BNC inputs, so a pair of BNC-RCA cables will get the job done for X-Y display work. This suspension computation simply runs as a single output channel. I also have a Digilent Analog Discovery 3 here, so we may try to use both USB 'scopes for the next blog after I figure out how to get the RCA jack output signals into it.

5. Analog Computation is running with all coefficients nominal and she's about to change the damping coefficient. *Andy Turudic | Electronic Design*

Running THAT is fairly straight forward. Simply select the Mode selector to "Coeff" and then go through each coefficient selection number and adjust the coefficient to the values in the patch schematic using the built-in panel voltmeter. The lack of a 10-turn pot in the design is a bit irritating, but it keeps costs way down and it's not too bad in sticking voltages to three digits of accuracy. Also, the value seems to hold if you come back to it after setting other coefficients.

Once that's done, just move the Mode selector to "Rep" (Repetitive") and play with the scope to get a Goldilocks display (there's a downloadable poster for scope setup, click here). If you're happy with the scope, the coefficients can then

6. Bob Pease's hardwired circuit schematic to compute the simple suspension system. Robert Pease | Electronic Design

Do you actually need an Analog Computer to simulate one problem? Not at all. It's just op amps, capacitors, resistors, and potentiometers, so you could build a bespoke circuit to solve a specific problem. This is what Bob Pease did for the automobile suspension he modeled out of discrete components. For your convenience, Figure 6 shows his schematic.

be changed with their respective pots to instantly compute the effects and results.

While the patching and the coefficient settings and twiddles are novice/kidfriendly, oscilloscope settings are likely to be the most frustrating part of it all where it's a good idea to have an adult with a bit of scope experience to get the scope display setup or at least be of age to use a guide to set it up.

An animated gif (*Electronic Design's* site doesn't support this way of showing demos yet, as I know some of you are firewalled from accessing YouTube) of my minion's damping coefficient potentiometer twiddles is hosted here.

#### Differentiating Methods of Solving Problems

Do you actually need an Analog Computer to simulate one problem? Not at all. It's just op amps, capacitors, resistors, and potentiometers, so you could build a bespoke circuit to solve a specific problem. This is what Bob Pease did for the automobile suspension he modeled out of discrete components. For your convenience, *Figure 6* shows his schematic (can

## Why Gamble on Your Passive Components? KOA Speer is All Aces!

KOA Speer is your ideal passive component partner. We offer a diverse and expanding family of surface mount and leaded resistors, as well as our Quality 1<sup>st</sup> mandate to deliver unmatched service and product quality... demonstrated by our 99%+ on-time performance despite shipping billions of resistors every month! Don't gamble on your passives, KOA Speer is all aces!

#### Go from Concept to Reality with THIN FILM PRECISION RESISTORS

- High reliability & high precision ideal for automotive & industrial applications

- Endurance at 85°C up to 3,000 hours

- RN73R, RN73H & WN73H

ISO 9001:2015 IATF16949:2016 you see where Bob cheated and inserted a differentiator into his circuit, which is a no-no for noise pickup, but then he pulls a Band-Aid out—leaky, weak, integrator to mitigate its effects?).

Is what Bob built an Analog Computer? Absolutely, yes! Is it programmable to solve other problems? Likely not, though I suppose you could use the same circuit, and the patch here to simulate a capacitor in series with a paralleled inductor and resistor. This is where a machine like THAT can be programmed with patchcords comes to shine. THAT can solve varying STEM problems, of varying sets and orders of equations, problems where the coefficients can be changed in real-time, without building new, bespoke, circuits.

We can simply pull the patchcords out of THAT and simulate something else with a new patchcord configuration. Or build upon an existing THAT patch if, for example, you wanted to add jerks to your simulation.

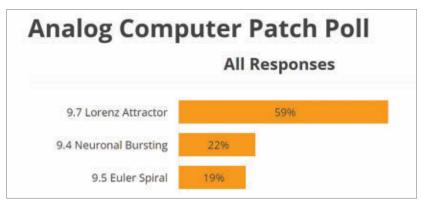

So, we have hardwired Analog Computing and then we have Programmable Analog Computing as with THAT. The THAT is so deceptively small that it can easily be used in your lap, especially when patching it while binge-streaming a really great Korean Medieval Soap Opera. The results of the poll from the last blog, on which patch you wanted to see in my next blog, are shown in *Figure 7*.

It looks like the reader choice for the next blog is the Lorenz Attractor. I'll set up that patch and run it for you next time.

So, we have hardwired Analog Computing and then we have Programmable Analog Computing as with THAT. The THAT is so deceptively small that it can easily be used in your lap, especially when patching it while bingestreaming a really great Korean Medieval Soap Opera. The results of the poll from the last blog, on which patch you wanted to see in my next blog, are shown in Figure 7.

Don't, however, expect me to explain it to you, lol, since I really do have a day job at this place that is, too often, orthogonal to being an engineer.

We will try to see if we can run The Attractor with a couple of different USB scopes, since I'll probably enlist my young apprentice to try to patch the computing solution at her place while her mother is again at work.

If you want your own THAT Analog Computer, don't forget that there's a discount code in my previous blog. Also recall that multiple THATs can be Master-Slaved to expand the number of compute elements that can be applied. The next part of this blog series is here.

All for now. —AndyT

*p.s.* There's a climate-change Easter egg in what I just wrote if you want something to seek to pass the time.

#### REFERENCE

1. The lead customer, testing and helping with product definition, of the IBM 360 was NASA—for the Apollo program. It, and Analog Computers not slide rules—is what put man on the moon: "In 1966, IBM announced the System/360 Model 91, the first computer system to feature out-of-order execution-the ability to automatically find concurrency in sequential code. For a time, the Model 91 installed at NASA's Goddard Space Flight Center was "the fastest, most powerful computer in user operation" — University of Michigan

\*Figs 1-3 Used with Permission. Copyright Anabrid GmbH. Unchanged content. Licensable under CC BY-NC 4.0

7. Poll results from Andy's last blog.

Trusted manufacturer by leading industry leaders for high quality Inductors and transformers Possessing **45** years of professional experience.

- High quality product with customization available

- Products are designed for various applications

- Automotive grade products are compliant with AEC-Q200

## New

Automotive series products Click for more information

Tel:+886-3-478-8188 Fax:+886-3-488-0648 Email: abcsa@atec-group.com www.atec-group.com JIM HANDY | General Director, Objective Analysis and TOM COUGHLIN | President, Coughlin Associates

## **New Memories** Making Meaningful Strides

Non-volatile technologies like MRAM and particularly ReRAM are poised to finally take a major leap into the embedded-memory design space.

**EVERY YEAR, ENORMOUS** effort is devoted to the development of new memory technologies, great advances are made, and fascinating new products and prototypes are introduced. So, why haven't these new memories become commonplace? Just to clarify, we're talking about memory technologies like MRAM, ReRAM, FRAM, and PCM. What's happening with all of these memories?

For those unfamiliar with those acronyms, let's spell them out. Just like today's leading memory technologies—DRAM, NAND flash, NOR flash, SRAM, and EEPROM—and the technologies that preceded them, specifically mask ROM and EPROM, the names stem from how they store bits. For the new memories. it's pretty straightforward:

- MRAM (magnetic RAM) uses magnetism to store the bit's state just like a hard drive, but without any moving parts.

- ReRAM (resistive RAM) stores a bit as a resistance, either high resistance or a low resistance. It's typically implemented as whether or not a metal filament runs through an insulator, or whether oxygen ions have been driven out of the insulator to form a conducting path.

- FRAM (ferroelectric RAM) is tricky, as it might imply that it's made out of iron ("ferro") or has magnetic properties similar to iron, but neither is the case. These memories simply exhibit a behavior whose I/V curve is shaped like the magnetization vs. field relationship of the magnetic hysteresis curve, so it got that name. These devices

typically store a bit by displacing an atom within a crystal.

• Finally, PCM (phase-change memory) uses the phases of a material to store a bit. If the material solidifies in a liquid phase, then resistance is high. If it solidifies in the solid phase, as a crystal, then its resistance is low.

These aren't really new technologies. FRAM has been around for over 70 years and PCM for over 50, but they're still waiting at the door, hoping for a chance to get into the memory market in a big way.

However, these non-volatile memories are starting to make a difference. In fact, the market is growing at a rate that should bring it to revenues of \$72 billion by 2034, with bit growth outstripping established technologies to bring it closer to the realm dominated today by NAND flash and DRAM.

#### Big Things are Happening in Embedded Memory

The biggest strides are being made in embedded memory, the memory in system-on-chips (SoCs)—microcontrollers, ASICs, and other chips that have been using NOR flash since it was invented in the 1980s.

Why would this be? Well, with the advent of the FinFET at 14 nm, flash memory was no longer an option. Of course, even if CMOS logic hadn't moved to a FinFET structure, 14 nm was out of the reach of planar flash anyway, for reasons we won't go into here. So, what were designers to do when they wanted on-chip non-volatile memory? For the short term, they took the memory off-chip and started using external SPI (Serial Protocol Interface) NOR chips to store programs, loading it into on-chip SRAM caches at boot-up. This works well, but it adds cost and consumes space.

The longer-term solution is to use a memory that can scale to processes smaller than NOR's 28-nm limit. Today, those are MRAM and ReRAM, but mostly MRAM. While that may change in the future, today MRAM is king, and it's starting to be seen in a number of wearable applications for health monitoring and other similar functions. Larger foundries offer it as an option to their standard CMOS logic processes, and more forward-thinking designers are embracing it with good results.

One key benefit is that the SoC's on-chip firmware can power down the memory, waking it up only when needed, saving a lot of energy during the time it's turned off. This is a benefit supported by all of these new technologies.

But something bigger is soon to happen. Like NOR flash, SRAM is also running into scaling issues. SRAM isn't shrinking as fast as the logic, and that prevents chips from shrinking in proportion to the process technology. This makes SRAM more and more expensive as time moves on.

While new memory technologies don't suffer from this problem, they're slower than SRAM. As a result, systems designers need to make some difficult decisions about how much nonvolatile memory (MRAM, ReRAM, FRAM, or PCM) to put onto the chip, and how much SRAM to use to cache this new memory for the performance to still reach its goals. Cache design is always a challenge, because sometimes big and slow beats fast and small. Even if SRAM scaled, this would be a concern, since new memories only require a single transistor to work, whereas SRAM needs six. Add to this the fact that firmware can also be optimized to the memory configuration, and you have quite the challenge due to so many variables.

In short, embedded SRAM is also threatened with replacement by a new memory. Such change is starting to move pretty fast. With it comes the promise of persistent memory in processor caches, and considerably lower energy consumption even in servers, bringing an altogether new look to computing of every kind.

Today MRAM is king, but ReRAM is poised to take its place. It's too early to know whether ReRAM or MRAM will win out as the dominant new non-volatile memory. However, if something interesting happens with FRAM or PCM, it could change everything.

#### Yes, But What of FRAM and PCM?

FRAM has been around for a very long time, since 1952, but it still hasn't gained much prominence, even though it has, by far, out-shipped all other new memory technologies combined. That's a surprise, because it's rarely discussed.