# <section-header><text><text>

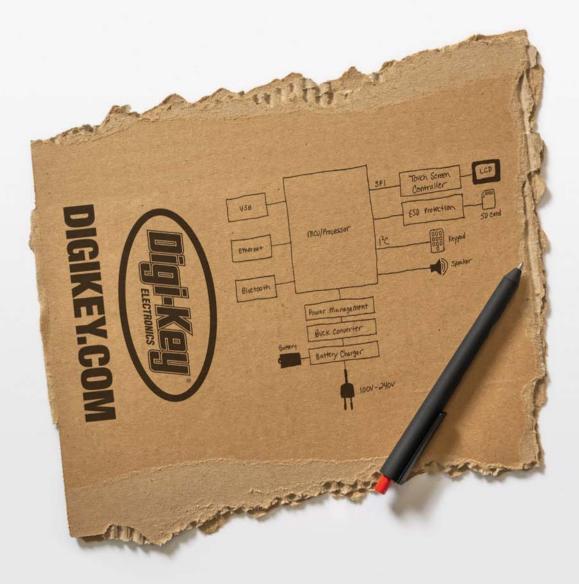

IDEAS START HERE Get inspired at digikey.com

The Engineering Unknown

# IDEAS start here

From millions of in-stock parts to the latest new product inventory, we've got everything you need to turn breakthrough ideas into reality.

Get inspired at **digikey.com** or call 1.800.344.4539.

Digi-Key is an authorized distributor for all supplier partners. New products added daily. Digi-Key and Digi-Key Electronics are registered trademarks of Digi-Key Electronics in the U.S. and other countries. © 2023 Digi-Key Electronics, 701 Brooks Ave. South, Thief River Falls, MN 56701, USA

# ebmpapst

engineering a better life

# AxiForce – Experience the future of fan technology.

The AxiForce tubeaxial fan series is ideal for keeping consistent, optimized temperature in control units for automation and other highly-modern technologies. Due to its variable installation, high cooling capacity in the smallest of spaces, and interactive integration into the device logic, it has already proven to be indispensable in modern automation. Now with the addition of our 80 mm, IP68 rated models AxiForce is even more versatile for the future.

Contact sales@us.ebmpapst.com for more info.

# ElectronicDesign.

# IN THIS ISSUE

# **FEATURES**

- 8 Lions, Chatbots and Generative AI, Oh My The population at large is enamored—and worried about generative AI. Are you?

- **Explainable AI for Anomaly Detection** 10 Explainable AI (XAI) can improve safety, security, and the overall user experience in IoT applications.

- 14 **11 Myths About Silicon Photonics**

By harnessing the basic properties of light and using photonics to speed computing, systems can be made that extend Moore's Law. However, myths have emerged about the technology.

- 22 How to Easily Design Power Supplies (Part 1) This article looks at the LDO and the switch-mode power supply. as well as the most common non-isolated topologies used for SMPS.

- Why are Specifications and Characterizations for 26 **Op Amps and FDAs Different and Confusing?**

- **Designing Noise-Free, High-Speed PCBs** 33

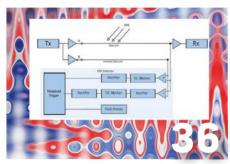

- 36 What's the Difference Between EMI and EMC in Electronic Designs?

Electromagnetic interference and electromagnetic compatibility are both important considerations when designing and working with electronic components and systems.

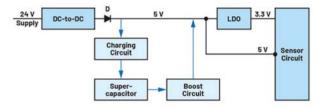

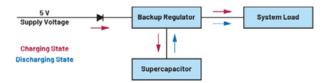

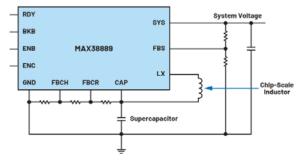

**Compact UPS with Supercap** 39

> Continuous supply voltage via an uninterruptible power supply is crucial for a number of applications, but it can be tough to ensure at all times.

# **COLUMNS & DEPARTMENTS**

6 Editorial

**Engineers Must Contend with** Generative AI

38 Ad Index

# 40 Lab Bench

EDITORIAL MISSION.

To provide the most current, accurate, and in-depth technical coverage of the key emerging technologies that engineers need to design tomorrow's products today.

FOLLOW US ON

FACEBOOK AND TWITTER

(ElectronicDesign)

(@ElectronicDesgn)

ELECTRONIC DESIGN (USPS Permit 172-080), (ISSN 0013-4872 print, ISSN 1944-9550 online) is published quarterly (Spring, Summer, Fall, Winter) by Endeavor Business Media, LLC. 1233 Janesville Ave., Fort Atkinson, WI 53538. Periodical postage paid at Fort Atkinson, WI, and additional mailing offices. POSTMASTER: Send address changes to Electronic Design, PO Box 2357, Northbrook, LE 600653257. SUBSCRIPTIONS: Publisher reserves the right to reject non-qualified subscriptions. Subscription prices: U.S. (\$75.00 per year); Canada/Mexico (\$112.50 per year); All other countries (\$150.00 per year). All subscriptions are payable in U.S. funds. Send subscription inquiries to Electronic Design, PO Box 3257, Northbrook, IL 60065-3257, Customer service can be reached toll-free at 877-382-9187 or at electronicdesign@omeda.com for magazine subscription assistance or questions.

### Printed in the USA. Copyright 2023 Endeavor Business Media, LLC. All rights reserved. No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopies, recordings, or any information storage or retrieval system without permission from the publisher. Endeavor Business Media, LLC does not assume and hereby disclaims any liability to any person or company for any loss or damage caused by errors or omissions in the material herein, regardless of whether such errors result from negligence, accident, or any other cause whatsoever. The views and opinions in the articles herein are not to be taken as official expressions of the publishers, unless so stated. The publishers do not warrant either expressly or by implication, the factual accuracy of the articles herein, nor do they so warrant any vi opinions by the authors of said articles.

Cover image.

281511893 © Alexander Kharchenko | Dreamstime.com

# Altach<sup>®</sup> In Stock Very Broad Selection of PCB Terminal Blocks Various Types, PIN Spacings and Ratings

# **Broad Selection of Quality**

FIXED PCB TERMINALS SCREW TERMINAL BLOCKS Wire Guard Type Lift Type Excenter Type SPRING TERMINAL BLOCKS Push-In Type Tension Spring Type Lift Type

# PLUGGABLE MULTI-CONNECTOR SCREW TERMINAL BLOCKS Wire Guard Type Lift Type Excenter Type SPRING TERMINAL BLOCKS Push-In Type Tension Spring Type PIN STRIPS

Custom Assemblies Available

#

# Time Saving **Push-In Technology** Easy wire insertion **No tool required !**

- Unique ergonomic design for quick and easy mounting

- 3.50, 3.81, 5.00 and 5.08mm pin spacing

- Screw flange version for additional stability

- Imprinting and coding available

# **State of the Art** TEST & MEASUREMENT

- Test Plugs

Test Sockets

- Alligator Clips

Test Probes

- Clamp-Type Test Probes

- Measuring Leads

- Measuring Sets

Altech Corp. Your Source for Automation & Control Components

AltechCorp.com | 908.806.9400

# A BETTER WAY TO UL & CSA<sup>™</sup>

Experts who help you from START TO FINISH

CE too!

# Design Consulting • Compliance Assistance Product Testing & Certification Lab

# CertifiGroup.com • 800-422-1651

# FREE UL-CSA-CE Compliance Whitepapers

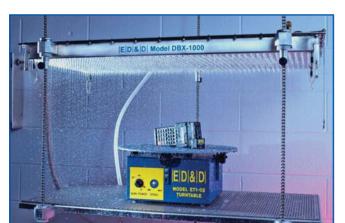

# **Product Safety Test Equipment**

ED&D, a world leader in Product Safety Test Equipment manufacturing, offers a full line of equipment for meeting various UL, IEC, CSA, CE, ASTM, MIL, and other standards. Product line covers categories such as hipot, leakage current, ground, force, impact, burn, temperature, access, ingress (IP code), cord flex, voltage, power, plastics, and others.

> ED&D 1-800-806-6236 • www.ProductSafeT.com

# Electronic Design.

# EDITORIAL

Senior Content Director: Bill Wong, bwong@endeavorb2b.com Senior Editor: David Maliniak, dmaliniak@endeavorb2b.com Managing Editor: Roger Engelke, rengelke@endeavorb2b.com Editor-at-Large: Alix Paultre, apaultre@endeavorb2b.com Senior Editor: James Morra, jmorra@endeavorb2b.com Technology Editor: Cabe Atwell, catwell@endeavorb2b.com

# CONTRIBUTING EDITORS

Lee Goldberg, Bill Schweber, Murray Slovick, Steve Taranovich

### ART DEPARTMENT

Group Design Director: Anthony Vitolo, tvitolo@endeavorb2b.com Art Director: Jocelyn Hartzog, jhartzog@endeavorb2b.com

# PRODUCTION

Production Manager: Brenda Wiley, *bwiley@endeavorb2b.com* Ad Services Manager: Deanna O'Byrne, *dobyrne@endeavorb2b.com*

# AUDIENCE MARKETING

User Marketing Manager: **Debbie Brady** *dmbrady@endeavorb2b.com* Article Reprints: *reprints@endeavorb2b.com*

# SUBSCRIPTION SERVICES

OMEDA, 847-559-7598 or 877-382-9187 electronicdesign@omeda.com

# LIST RENTAL

List Rentals/Smartreach Client Services Manager: Mary Ralicki mralicki@endeavorb2b.com

# SALES & MARKETING

Gregory Montgomery, gmontgomery@endeavorb2b.com AZ, NM, TX  $\,$

Jamie Allen, jallen@endeavorb2b.com AL, AR, SOUTHERN CA, CO, FL, GA, HI, IA, ID, IL, IN, KS, KY, LA, MI, MN, MO, MS, MT, NC, ND, NE, OH, OK, SC, SD, TN, UT, VA, WI, WV, WY, CENTRAL CANADA

Elizabeth Eldridge, eeldridge@endeavorb2b.com CT, DE, MA, MD, ME, NH, NJ, NY, PA, RI, VT, EASTERN CANADA

Stuart Bowen, sbowen@endeavorb2b.com AK, NORTHERN CA, NV, OR, WA, WESTERN CANADA AUSTRIA, BELGIUM, FRANCE, GERMANY, LUXEMBURG, NETHERLANDS, PORTUGAL, SCANDINAVIA, SPAIN, SWITZERLAND, UNITED KINGDOM

Diego Casiraghi, diego@casiraghi-adv.com ITALY

Helen Lai, helen@twoway-com.com PAN-ASIA

Charles Liu, liu@twoway-com.com PAN-ASIA

### DIGITAL

VP of Digital & Data Innovation: Ryan Malec, rmalec@endeavorb2b.com

# ENDEAVOR BUSINESS MEDIA, LLC

30 Burton Hills Blvd, Ste. 185, Nashville, TN 37215 | 800-547-7377 www.endeavorbusinessmedia.com

CEO: Chris Ferrell President: June Griffin CFO: Mark Zadell COO: Patrick Rains CRO: Reggie Lawrence

Chief Digital Office: Jacquie Niemiec

Chief Administrative and Legal Officer: Tracy Kane

### **DESIGN & ENGINEERING GROUP**

EVP, Design & Engineering Group: Tracy Smith, tsmith@endeavorb2b.com Group Content Director: Michelle Kopier, mkopier@endeavorb2b.com

Electronic Design, Machine Design, Microwaves & RF, Power & Motion, SourceESB, Source Today, 3DX

# Altach® LARGEST Selection of DIN ENCLOSURES 8 Series With Over 240 Types

KS4400 Series

......

KU4000 Series

KU4100 Series

K04700 Series

DIN Rail and Panel Mount

Integral PC Board Guides

Many terminal to PCB

connection options

Fixed and Pluggable Terminals

....

\*\*\*\*\*\*\*

KS4400 Series

1

H

A BLEELE

FRANK

K70 Series

K04070 Series

Multi-functional Enclosure System

> KV4600 Series

AltechCorp.com | 908.806.9400

# Transformers & Inductors SURFACE MOUNT (and thru-hole)

20

ANAB ISO 9

1310

# Size Does matter!

Low Profile From .18" Height 1.2 Grams Weight

# **Reliability:**

MIL PRF27/MIL PRF21308 Manufacturing Approved DSCC

Quality: AS9100C Qualified Facility

US Manufactured Military and Commercial Aircraft Supplier for over 50 Years

> For all your TRANSFORMER & INDUCTOR requirements • Audio • Pulse • DC-DC • MultiPlex • Power & EMI

See Pico's full Catalog immediately at www.picoelectronics.com

800 431-1064 Fax 914-738-8225 E Mail: info@picoelectronics.com

Editorial BILL WONG | Senior Content Director bwong@endeavorb2b.com

# Engineers Must Contend with **Generative Al**

Whether we like it or not, we need to deal with all sorts of machine-learning models, including generative AI.

**IT SEEMS THAT** artificial intelligence and machine learning (AI/ML) is becoming as ubiquitous as the internet. Even the U.S. Congress is talking about it, or at least around it. Bad actors use AI/ML to create more nefarious attacks while companies are incorporating it into their products and algorithms. People utilize it daily and often unknowingly to crop someone out of a photo or when searching for someplace to eat.

Much of what AI/ML does these days is improve on tasks that are performed daily, but faster and often better. The photo of my aquarium has two added fish (*see figure*). One was from another photograph while the other was created using generative AI. Do you know which is which? I used the open-source Gimp image editor to create the final photo so that the two Siamese Fighting fish stand out. However, I could have done more to make them blend in or even used AI tools to accomplish that.

This type of graphic manipulation is only the tip of the iceberg, but one that almost anyone can use. The other tools garnering major interest are chatbots like OpenAI's ChatGPT and Google's Bard. A number of issues have arisen from the source of training material for these large-language-model (LLM) tools regarding bias and explainability. There are also discussions about legal, moral, and liability issues when it comes to using any output associated with these tools.

These days, we at *Electronic Design* are making sure we annotate the source of our images. However, that's not the case for many websites. Likewise, we're not using generative AI to create articles as some sites are doing. Some of those sites indicate when AI is utilized, though not always, and do you even care?

Engineers may be able to overlook these issues if it were limited to images, videos, and text, but the basic AI/ML technologies are part of the software we use to create applications and products from chips to software. Eventually, these aspects of the tool will not be something that can be avoided as these models and technologies are intimately included within the tool.

The technology in general has the potential to vastly improve the output and capabilities of engineers and programmers. Nevertheless, like the rise of security tools and technologies, taking advantage of AI/ML will require a better understanding of the capabilities and liabilities of AI/ML-based tools. Stay tuned for more on this subject.

The background is a photograph of my aquarium, but one of the two Siamese Fighting fish is Al-generated while the other is a from a photograph. *William Wong, Al Yupiramos Group – Dreamstime, Utalert - Dreamstime*

# The (lowest) Loss Leaders

XGL Family power inductors feature the industry's lowest DC resistance and extremely low AC losses for a wide range of DC-DC converters

Coilcraft XGL Family molded power inductors are available in a wide range of sizes, with inductance values from 82 nH to 56  $\mu$ H and current ratings up to 117 Amps. With up to 60% lower DCR than previous generation products, they are the most efficient power inductors available today!

Their ultra-low DCR and higher Irms also allow XGL Family inductors to operate

much cooler than other components.

All XGL Family inductors are qualified to AEC-Q200 Grade 1 standards (with a maximum part temperature of 165°C) and have no thermal aging issues, making them ideal for automotive and other harsh environment applications.

Download the datasheets and request free samples at **www.coilcraft.com/XGL**.

The population at large is enamored—and worried—about generative AI. Are you?

he challenge with artificial intelligence (AI) since its inception has been one of hyperbole versus actuality. AI in literature abounds with things like Asimov's three laws of robotics and positronic brains. Androids and intelligent machines were once stuff of science fiction, but these days we at least to appear to have this capability.

For instance, we have Working Dog[Bot]s that can operate autonomously. The Ghost Robotics Vision 60 quadruped robot can climb stairs and even slide across ice. It's able to recognize objects and knows how to find the charger when its battery runs low.

There are humanoid robots that can converse in multiple languages while maintaining eye contact. We have smart speakers that can answer questions and pull from a massive cache of data to let you know what time it is in Marrakesh.

The problem is that we are still light years away from anything close to an android like Data from *Star Trek: The Next Generation* or C3PO from *Star Wars*. This isn't to say we couldn't build something that closely resembles those androids, but the result is rather disappointing once you try to challenge them with even simple tasks.

# Worrying About Generative AI

Machine learning (ML) is a subset of AI, although many use the terms interchangeably. I do, often to the chagrin of readers. ML tools cover a lot of ground, and different machine-learning models and methodologies have been created to address a host of different tasks. Models that work well to identify things in images don't necessarily work well when it comes to understanding the spoken word.

Utilization of focused ML models has changed the way we look at visual problems like advanced driver-assistance systems (ADAS), self-driving cars, and autonomous robots. Recognizing objects in real-time and providing this type of information is relatively simple these days. However, acting on that information is a bit more of a challenge, though it's being addressed albeit with different models and approaches. Generative AI is one of these approaches. Generative pre-trained transformer (GPT) models are also referred to as large language models (LLMs). They're collectively known as chatbots, one of which is the well-known ChatGPT.

The approach can be used for many applications, but those of note tend to be based on very large data sets, often scraped from the internet, that can interact with queries posted by users. They provide a similar interactive interface that harkens back to the ELIZA computer therapist computer program created by Joseph Weizenbaum from MIT back in the 1960s. It didn't use a GPT model but rather a ruleset.

ELIZA garnered lots of interest due to its interactive nature and it could be convincing, to a point. Chatbots today are more effective and have a better understanding of some of the material they're trained with, but only within the limits of the model and training. The results from interacting with programs like ChatGPT range from insightful to silly.

Keep in mind that chatbot applications these days are doing quite a bit, from per-

forming natural language processing of input, to analyzing a request, to finding and forming a response and presenting it in a natural language format. It would be trivial to make this work with audio inputs and outputs, which would wow some users. From a technical standpoint, though, it's just a design exercise.

# Jobs at Risk?

The more focused the application, training, training data, and models, the better the results. One worry carried by many is that a suitable training model could replace them. It could be anyone from a programmer to a tech support specialist to a bond trader.

It's not just generative AI that's at issue when considering whether to worry about AI taking over the world. Many "AI applications" are actually collections of different models, tools, and regular programming that perform a job. This might involve creating a new music score or software program, or handling an order for burgers and fries. The thing is that someone helped develop the application and used AI-related tools to create the application or incorporated the AI support into it to make it work.

Those creating the application tend to have an understanding about AI that ranges from minimal to expert level, but at the least, they understand the limits and capabilities of the system. Users and managers often have a much different view and understanding of these limits and capabilities and their potential impact.

I tend to be much more worried about the human side of the equation when it comes to utilization and deployment of AI tools and models due to the lack of understanding of those simply using a tool or application. It's akin to the meme "It's on the internet, so it must be true."

Unfortunately, most AI is not analogous to a calculator that will always provide a correct answer to a basic problem, like adding numbers. AI usually is related more to statistics, and we know how well most people understand statistics.

# **Fact or Fiction?**

The challenge is that many will wind up using tools for less than noble reasons. The ability to generate a paper on a topic or create an image or video by specifying incorrect facts can result in data like a video that's completely false or skewed far from the truth. In fact, ML models are often used for optimization—optimizing for a lie works as well as optimizing for the truth.

There seems to a great deal of worry surrounding the misuse of AI technology, and that we should somehow slow down research in this area. I contend that the problem of people using the technology is at issue rather than the technology itself.

Creating videos of events that didn't occur is what most movies are all about. Writing stories that are fiction is the norm. The ability to do these things in the past was possible, but it was typically timeconsuming and often required a level of expertise that would be beyond most people. Generative AI tools have simply lowered the bar of entry while drastically improving the quality of the results.

Not only are these tools being made available on a regular basis. but they're on platforms like smartphones. Editing someone out of a picture or adding someone else is now a tap or two away.

# Taking Advantage of Generative AI

I regularly receive press releases about new products touting the fact that they utilize or present ML tech, especially generative AI or chatbots. This isn't surprising given the hype. However, it's also about the capabilities of these tools, since it's not just smoke and mirrors. Generative AI can be very useful and augment the users' use of an application or improve how the application works.

From a developer's perspective, the how and why become important. For example, can an interactive chatbot improve areas of a particular application? General help support comes to mind, but a host of other features could be readily apparent, from reducing the number of options presented to the user to finding possible solutions within a large list of possibilities (e.g., finding the right transistor or chip for a particular task).

Keep in mind that one needn't utilize generative AI tools or application support if it's not warranted. However, taking a new look at your development process or application with a better understanding of what's possible may be very worthwhile.

There are multiple areas in which a developer may find ML useful. These include application development, design, implementation, delivery, tech and user support, as well as long-term maintenance. Much of this tends to be application-specific, although the development and design is often more standard and utilizes third-party tools.

Incorporating ML into an application or its support requires a much better understanding of the ML support that's available. GPT may not be a good choice, but other ML models and tools might be better options.

Other significant costs are involved as well, from startup, to training of developers, to training of models that come into play. These can be justified if they improve the quality or functionality of the development process or application. If not, they may be a gold ring that's not worth wearing.

Developers need to keep in mind not only the possibilities that tools like GPT can provide, but also the potential limitations. For example, what will be the false positive and negative rates? Will they be significant? Will a customer be faulted, hurt, etc. because of results that might be subpar? Is there sufficient training data? Will training be an ongoing process? How will using ML and GPT affect support and security? How will the system be tested and verified?

The latter brings into play details like explainability, the ability for an ML model/system to provide a description of the results, how they were arrived at, and how they're justified.

P.S. I still haven't figured out how to get a lion into the article so that I could use it in the title. Guess I should have asked a chatbot.

# **Technology Report**

GILABRAHAM | Business Development Director and Product Marketing, CEVA Artificial Intelligence and Vision

# **Explainable AI** for Anomaly Detection

Explainable AI (XAI) can improve safety, security, and the overall user experience in IoT applications.

nomaly detection is the process of identifying when something deviates from the usual and expected. If an anomaly can be detected early enough, relevant corrective action can be taken to avoid serious consequences. As children, we have played the game of who can identify the oddities in a cleverly composed picture. This is anomaly detection at play.

Engineers, scientists, and technologists have historically counted on anomaly detection to prevent industrial accidents, stop financial fraud, intervene early to address health risks, etc. Traditionally, anomaly-detection systems have relied on statistical techniques, predefined rules, and/or human expertise. But these approaches have their limitations in terms of scalability, adaptability, and accuracy.

The number of real-life, high-value use cases for AI anomaly detection have grown a lot over the years and are expected to continue to rise. Advances in artificial intelligence (AI) are revolutionizing the field of anomaly detection. The result is improved accuracy, faster detection, reduced false positives, scalability, and cost-effectiveness. This article will identify what's needed to implement such solutions and will touch on some use cases for illustrative purposes.

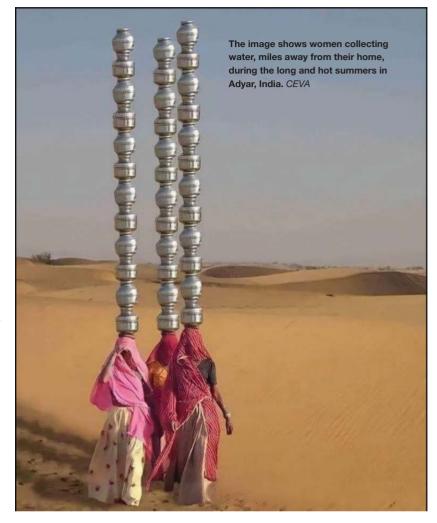

These days, many of the anomalies we come across may not be just happenstance but rather human-created with malicious intent. For example, social media is rife with images and videos that are fake and deepfake. Advanced graphics and video production and manipulation technologies have made this possible. Let's take a simple example and play the game of spotting the oddities on a modern day picture that was found on social media.

Study the *figure* (p. 11) and carefully and note down things that are anomalous.

Will traditional techniques for AI anomaly detection work on this picture? Maybe. One's knowledge of the place referenced in the caption, common sense, knowledge of physics principles, practicality perspective, etc., could help identify the anomalies in the picture. Based on that, one could declare the picture to be genuine or fakery. However, that's not enough for others to believe your conclusion. You need to be able to explain how you came to that conclusion. This is the explainability part and it's essential.

# What is Explainable Artificial Intelligence (XAI)?

XAI is a subset of AI that emphasizes the transparency and interpretability of machine-learning models. With XAI, the output or decision of the AI model can be explained and understood by humans, making it easier to trust and utilize the results.

Anomaly detection using XAI can help identify and understand the cause of anomalies, leading to better countermeasure decision-making and improved system performance. The key benefits of XAI for anomaly detection are its ability to handle complex datasets, improve accuracy, and reduce false positives and false negatives.

# What are the Different Use Cases for XAI?

AI anomaly-detection systems may make decisions that have significant impacts on individuals and the social collective at large. Many use cases are on the edge AI applications that relate to security, safety, production-line longevity, and customer-friendly service.

Furthermore, bottom-line decisions without reasoning are somewhat useless for use cases that will penetrate the judicial system and medical prognosis services in the future. XAI provides a way for systems to illustrate the decision-making process, as well as learn and continually improve for the benefit of industry and society.

# Use Case: Access Control (Facial Recognition)

Authentication by facial-recognition applications is widely used for access control purposes and relies on computer vision and AI. While a system may be very good at detecting faces, many unexpected factors may cause the system to fail to recognize a face.

Given the purpose of this application, it's tuned to prevent false-positives and alert if a malicious breaching attempt is taking place. But for a user who knows that his face should be recognized, it's very annoying to say the least. Perhaps the application was running into difficulty near the mouth area or around the eyes. XAI can communicate accordingly so the user can retry after removing the mask or the glasses.

AI systems are learning-oriented and count on feedback for continual improvements to their algorithms. The system may be able to improve itself and recognize this user the next time around, even with partial occlusion of the face. On the other hand, XAI is enabling the system to distinguish at all times between recognition failure and intentional breaching attempt and alert accordingly.

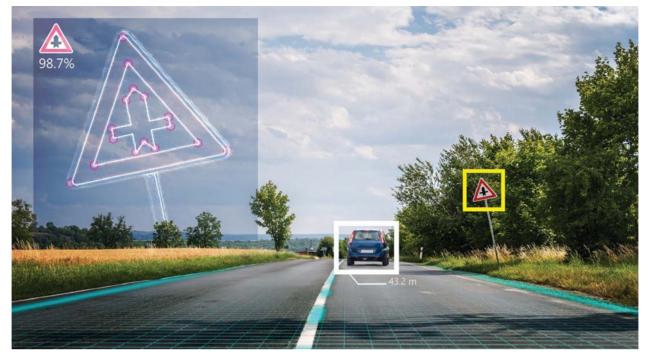

# Use Case: Autonomous Driving TSR (Traffic Signs Recognition)

Autonomous driving uses computer vision and AI to recognize speed limits and act accordingly. What if a malicious actor or natural deterioration were to alter a sign to change it from say 60 mph to 600 mph or to 80 mph? This use case can be more challenging than the facial-recognition case.

The 600-mph sign could be easily ignored as a tampered sign as no roadbased vehicle of current times can even come close to 600 mph. But the 80-mph sign is easily achievable by many vehicles and it's a legitimate speed limit in many places on many roads. However, if the sign was fake, acting accordingly may not only be illegal, but also dangerous due to special road conditions. XAI could determine the validity of a sign, provide a probability level to the conclusion, and explain how that was arrived at. The autonomous-vehicle system could then take a safe action based on that input.

# *Use Case: Monitoring the Health of a Factory Machine*

A factory machine that stops working unexpectedly and abruptly could be economically very expensive for a business. To avoid such a situation, sensors placed in the machine would continuously monitor the sounds emanating from the machine and run AI network models to analyze and detect abnormalities.

If out-of-order sounds or irregular frequencies are detected, which may lead to mechanical problems, the technician would be alerted to take preventative action before an abrupt breakdown of the machine.

# *Futuristic Use Case: Enabling Legal Hearings and Sentencing*

There's talk about using AI to analyze legal cases and issue verdicts. By analyzing legal documents and historical data, AI can identify anomalies in the data that may be relevant to the case.

With human judges, the most important aspect is the reasoning found in the opinion piece written after the case has been heard. By using XAI, the system can explain the anomalies identified, which can lead to better decision-making and improved overall system performance. For example, the use of XAI can help to identify the reasons why a particular legal precedent wasn't used in a case.

# What are the Tech Requirements for Implementing XAI?

Most XAI-driven anomaly-detection use cases require excellent computer vision, sound analysis, sensor-fusion capabilities, and multiple AI network models. For example, in the facial-recognition use case, parallel to the main AI network model that detects and authenticates specific individuals it's trained to recognize, a relatively lean network will run only over a minimal region of interest (ROI) that was detected and authenticated positive.

# he purpose of the secondary network is to run anomaly detection and genuine check to prevent a system breach through DeepFake and others.

The purpose of the secondary network is to run anomaly detection and genuine check to prevent a system breach through deepfake and others. This process overhead must be optimized to minimize power consumption, and therefore will run mixed precision network on selective frames, ROI, and only over selective input/ output layers from the main network.

The latter flow is somewhat different from traditional use cases, thus requiring a flexible memory architecture and adaptive data flow between the different AI processor blocks. When authentication negative or a genuine issue is detected, a larger XAI model will come forward to identify the issues that caused the fail and pass that information to the application layer for further action.

# How is AXI Implemented?

Most of the AI anomaly-detection use cases are typically on edge AI applications. Anomalies need to be quickly detected, and then identify the cause and report it accordingly to take appropriate corrective actions in real-time.

An AI processor that can run multiple AI networks in parallel and perform computer-vision analysis, as well within the processor itself, is key. Depending on the use case and application, part of an AI network may have to be run, followed by statistical analysis on the subject image or sensing element. This may be followed by manipulation of the image. Then the rest of the first network or another AI network is run to explain the anomaly reason.

Thus, the implementation of XAI requires a powerful processor that offers the following:

- Highly flexible AI processor to implement diverse XAI/ML processing flows: memory architecture, multi-engine structure.

- High-performance computing capabilities: support for multiple data types including low-precision arithmetic operations; highly parallel processing capabilities; advanced quantization capabilities.

- Support the latest neural-network architectures.

- High utilization for efficient power consumption.

- Built-in computer-vision/DSP processing capabilities.

- Support mixed precision inferencing for data and weights.

# CEVA Processor for Implementing XAI

One example of a platform designed to run XAI networks is CEVA's NeuPro-M AI processor. The NeuPro-M processor core can be chosen in configurations of up to eight engines, each with its own vision DSP processor. As a result, there's no need for the application to reach for an external DSP, GPU, or CPU for image processing.

Depending on the application need, the configuration with the appropriate number of engines can be selected to enable that many different AI networks to be run. The engines support various neural-network architectures and quantization capabilities.

An application can implement some network layers in 16-bit, some in 8-bit, etc. In certain situations, even 2-bit implementations are possible. This flexibility not only saves power and area, but also accelerates performance, all of which are critical for edge AI use cases. NeuPro-M supports mixed precision as well, e.g., data and weight.

# Fast Pulse Test Systems from Avtech

Avtech offers over 500 standard models of high-speed pulsers, drivers, and amplifiers ideal for both R&D and automated factory-floor testing. Some of our standard models include:

| AVR-E3-B:                                                                | 500 ps rise time,<br>100 Volt pulser                   |                           |  |  |

|--------------------------------------------------------------------------|--------------------------------------------------------|---------------------------|--|--|

| AVRQ-5-B:                                                                | Optocoupler CMTI<br>tests, >120 kV/us                  |                           |  |  |

| AVOZ-D6-B:                                                               | 1000V / 200A,<br>1-10 us pulser                        | t <sub>r</sub> = 450 ps   |  |  |

| AV-1010-B:                                                               | General purpose<br>100V, 1 MHz<br>pulser               | 50 V/DIV                  |  |  |

| AVO-9A-B:                                                                | 200 ps t <sub>r</sub> , 200 mA<br>laser diode driver   | 5 ns/DIV<br>AVR-E3-B      |  |  |

| AV-156F-B:                                                               | 10 Amp current<br>pulser for airbag<br>initiator tests |                           |  |  |

|                                                                          | AVTEO<br>Nanosecond<br>Since                           | Electronics               |  |  |

| Pricing, manuals, datasheets and test results at:<br>www.avtechpulse.com |                                                        |                           |  |  |

| US & Cana                                                                | AVTECH ELECTR<br>da 888-670-8729,<br>info@avtect       | Worldwide +1-613-686-6675 |  |  |

# Pulsed Laser Diode Drivers from Avtech

Each of the 18 models in the Avtech **AVO-9 Series** of pulsed laser diode drivers includes a replaceable output module with an ultra-high-speed socket, suitable for use with sub-nanosecond pulses.

Models with maximum pulse currents of 0.2A to >10A are available, with pulse widths from 400 ps to 1 us.

th 40 mA/DIV 1 ns/DIV Model AVO-9A-B

GPIB, RS-232, and Ethernet control available.

Nanosecond Electronics Since 1975

Pricing, manuals, datasheets and test results at: www.avtechpulse.com/laser

AVTECH ELECTROSYSTEMS LTD. US & Canada 888-670-8729, Worldwide +1-613-686-6675 info@avtechpulse.com

# High Output - Low Risetime Pulsers from Avtech

Nanosecond and faster pulsers covering a wide range of amplitudes! GPIB / RS-232 / Ethernet standard on "-B" models. Standard and customized models available.

# Ampl t<sub>RISE</sub> Max. PRF Model

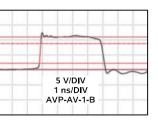

| 5 V   | 00 ps  |         | AVF-AV-13-C           |

|-------|--------|---------|-----------------------|

| 10 V  | 120 ps | 1 MHz   | AVP-AV-1-B            |

| 20 V  | 120 ps | 1 MHz   | AVP-AV-HV2-B          |

| 20 V  | 200 ps | 10 MHz  | AVMR-2D-B             |

| 40 V  | 150 ps | 1 MHz   | AVP-AV <b>-</b> HV3-B |

| 50 V  | 500 ps | 1 MHz   | AVR-E5-B              |

| 100 V | 500 ps | 100 kHz | AVR-E3-B              |

| 100 V | 300 ps | 20 kHz  | AVI-V-HV2A-B          |

| 200 V | 1 ns   | 50 kHz  | AVIR-1-B              |

| 200 V | 2 ns   | 20 kHz  | AVIR-4D-B             |

| 400 V | 2.5 ns | 2 kHz   | AVL-5-B-TR            |

|       |        |         |                       |

Nanosecond Electronics Since 1975

Pricing, manuals, datasheets and test results at: www.avtechpulse.com AVTECH ELECTROSYSTEMS LTD. US & Canada 888-670-8729, Worldwide +1-613-686-6675 info@avtechpulse.com

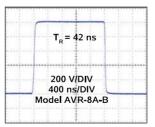

# 100 to 1000 Volt Lab Pulsers

Avtech offers a full line of 100, 200, 500, 700 and 1000 Volt user-friendly pulsers capable of driving impedances of 50  $\Omega$  and higher. The **AVR Series** is suitable for semiconductor and laser diode characterization, time-of-flight applications, attenuator testing, and other applications requiring 10, 20, or 50 ns rise times, pulse widths from 100 ns to 100 us, and PRFs up to 100 kHz. GPIB, RS-232, and Ethernet ports are standard.

See additional test results at: http://www.avtechpulse.com/medium

Pricing, manuals, datasheets and test results at: www.avtechpulse.com/medium AVTECH ELECTROSYSTEMS LTD. US & Canada 888-670-8729, Worldwide +1-613-686-6675 info@avtechpulse.com

# **11 MYTHS** About Silicon Photonics

By harnessing the basic properties of light and using photonics to speed computing, systems can be made that extend Moore's Law. However, myths have emerged about the technology. This article debunks them, setting the record straight.

ilicon photonics is a technology that uses silicon-based materials to manipulate and transmit light to create lowerlatency compute and interconnect solutions. One of the main advantages is its ability to integrate optical components onto a single package with electronic components. This allows for the creation of highly integrated systems that can process both electronic and optical signals, potentially leading to more efficient and compact devices.

Many misconceptions abound about how to use photonics to enhance today's designs. Its potential is understood, but is it ready to be deployed? Overall, the value of silicon photonics lies in its potential to enable new technologies and applications that were previously not possible with traditional electronic circuitry, as well as to improve the efficiency and performance of existing technologies. So, what myths have emerged? We look at 11 of them, and present the evidence to debunk them.

# **1.** Nice research project, not commercially viable today.

Silicon photonics has been gaining interest in recent years due to its potential to offer high-speed data transfer, increased bandwidth to memory, and low-power consumption. While some challenges are still associated with its implementation, silicon photonics has already shown promising commercial viability in various applications (*see figure*).

One application is in data-center interconnects, where it can offer high bandwidth, low latency, low power consumption, and rack-to-rack connections. High-speed copper connections have length limitations without using repeaters. Silicon photonics can improve datacenter interconnect by providing lowerlatency Compute Express Link (CXL) connections between servers, GPUs, and memory pools.

The use of standard CMOS fabrication processes for silicon photonics may be able to reduce the cost and complexity of manufacturing, making it a more viable commercial solution.

# 2. CMOS will continue to scale according to Moore's Law.

Since the start of the semiconductor industry, computing power improvement can be described by Moore's Law: Transistor density doubles every 18 months, enabling CMOS chips to continuously improve computing power while maintaining constant energy and area consumption.

As the chip manufacturing process moves to 5 nm and 3 nm, transistor density is close to its physical limit. Moore's Law is slowing down and the traditional single-chip computing power improvement path is unsustainable. Silicon photonics is a technology that will allow scaling to continue beyond the limits of Moore's Law. Digital chips are now limited by the physical limits of the underlying component—the CMOS transistor. Optical signals and devices follow different physical principles. The interactions of optical signals are typically linear and can be mapped as linear calculations. They should enable optical compute accelerators to outperform CPUs and GPUs over time.

# **3.** Silicon-photonics use cases are very narrow.

Silicon photonics is a technology that uses silicon as a platform for the generation, manipulation, and detection of light. It's a mature technology in telecom and data-center applications for transporting information over fiber connections.

It's now applied to other compute needs, where high bandwidth and low latency are required for scaling systems and has the potential to revolutionize a wide range of industries.

Some applications include:

- Data-center interconnects to transmit large amounts of data over long distances at high speeds.

- High-performance computing to connect multiple processors together, enabling faster data transfer and reduction of I/O bandwidth to large memory pools.

- Telecommunications networks to increase capacity and speed of data transmission.

- LiDAR systems for self-driving cars and other autonomous vehicles, enabling precise and accurate distance measurements.

- Quantum computing to control and manipulate qubits, opening the door to faster and more efficient quantum computations.

# **4.** Photonics requires a significant shift in methodology.

Leveraging silicon photonics requires extending the existing methodology from traditional electronics to photonics. In electronics, the information is transmitted and processed using electrons. In photonics, information is transmitted and processed using light. Fabricating photonic ICs will require a different set of design rules, fabrication processes, and testing methodologies.

Using photonic ICs in a system leverages existing methodologies and design rules. Many photonic ICs use electronic ICs in a co-packaged configuration to translate electrical signals to optical signals and back to electrical signals. The application is transparent to the system designer since the optical signals are internal to the device.

# 5. Implementing silicon photonics would require a steep learning curve for adoption.

The learning curve to fabricate silicon photonic devices is not as steep as other emerging technologies. Silicon photonics involves the integration of multiple disciplines, including electronics, optics, materials science, and fabrication techniques.

Adopting silicon-photonics ICs is similar to electronic ICs since the photonic ICs are generally co-packaged with electronic ICs. These ICs typically have electrical interfaces and behave similarly to other ICs in the design of a system.

# 6. Digital ICs and photonic ICs are hard to integrate.

Integrating digital and photonic ICs is possible, and it's been proven by several

companies producing photonic ICs using a hybrid approach to ensure their reliability and performance.

A hybrid integration approach is often employed to integrate electronic and photonic ICs by fabricating digital and photonic circuits separately and then bonding them together. This can be done using various techniques, such as flip-chip bonding, wire bonding, or solder bonding.

The design and fabrication of hybrid ICs requires careful consideration of several factors, including thermal management, electrical and optical coupling, and packaging. Because digital circuits can generate a significant amount of heat that can affect the performance of photonic circuits, thermal management is critical to ensure the reliability and stability of the ICs.

# 7. Artificial-intelligence/ machine-learning (AI/ML) workloads will continue to scale on GPUs.

AI/ML workloads scale on GPUs without the use of photonics and are the workhorse of AI/ML training due to their ability to handle parallel-processing tasks, critical for training large models. Thanks to recent improvements in GPU performance, they can handle increasingly complex AI/ML workloads.

However, as AI/ML workloads continue to grow in complexity and size, faster and more efficient data transfer is needed between GPUs and other processing units. This is where photonics can play a role by enabling high-speed, low-latency interconnects between GPUs, CPUs, and other processing units to boost efficiency and data-transfer speed.

As AI/ML models become more complex, specialized hardware accelerators, such as tensor processing units (TPUs) and field-programmable gate arrays (FPGAs), will be required. These accelerators can use silicon photonics for efficient interconnects and data transfer via low-latency CXL connections.

In addition, new photonic accelerators use low-latency optical NoCs (optical network-on-chip or oNoC) to increase performance and throughput of AI workloads. For specific functions, these accelerators are up to 800X faster than the most advanced GPUs.

# 8. Digital chips at 3 nm have better performance.

It's difficult to directly compare the performance of digital chips at 3 nm and silicon-photonics chips because they're designed for different applications and use different metrics to measure performance. The choice depends on the specific application requirements and design considerations.

Digital chips at 3 nm are designed to process digital information, such as performing arithmetic operations, logic functions, and memory operations. They're optimized for high-speed computation and low-power consumption, which is critical for applications such as mobile devices, data centers, and high-performance computing.

Silicon-photonics chips are designed primarily for transmitting and processing optical signals. They're optimized for t's difficult to directly compare the performance of digital chips at 3 nm and siliconphotonics chips because they're designed for different applications and use different metrics to measure performance.

high-speed data transfer and low-power consumption, critical for applications such as data communication, sensing, and medical imaging.

While digital chips at 3 nm may have better performance than silicon-photonics chips for digital processing tasks, siliconphotonics chips have the potential to offer higher bandwidth and lower latency for data transfer over longer distances. For example, photonics can be used to improve a digital chip's access to memory and significantly reduce the memory I/O bottleneck. In addition, silicon-photonics chips can offer higher energy efficiency for certain applications in which reducing power consumption is critical.

# 9. Optical NoCs are too small to be practical.

Optical NoCs have the potential to offer high-bandwidth and low-latency communication between on-chip processing units. The practicality depends on various factors, such as cost, power consumption, reliability, and scalability.

The cost of implementing an optical NoC requires specialized components e.g., lasers, modulators, and detectors that can be expensive to manufacture and integrate. While optical communication may offer low-power consumption compared to electrical communication, the power consumption of optical components, such as lasers and modulators, still often runs high.

Optical NoCs hold several key advantages over their digital counterparts. Since connections between the digital chips use light, oNoCs are extremely low latency and can communicate with all nodes across the device at the same time. This solves the nearest-neighbor problem with digital ICs and enables new topologies to be considered.

Unlike digital NoCs, oNoCs aren't limited to a single reticle. With wafer stitching, oNoCs can provide wafer-scale density when using standards like the Universal Chiplet Interconnect Express (UCIe) for the digital interfaces between chiplets.

# **10.** CXL is fine with copper interconnect, not optical interconnects.

CXL is a high-speed interconnect standard designed to enable communication between CPUs, GPUs, memory, and other processing units. While the initial versions of CXL use electrical interconnects, utilizing optical interconnects for CXL beyond a meter is growing in interest.

Optical interconnects can offer higher bandwidth, lower latency, and lower power consumption compared to electrical interconnects, especially over longer distances. Using optical interconnects for CXL beyond a meter can also enable more flexible system design and deployment. With optical interconnects, processing units may be placed further apart, allowing for more flexible system configurations and reducing the need for complex cabling.

# **11.** Other technologies are more promising.

Silicon photonics is being used for high-speed interconnects in computing systems, including interconnects between processors, memory, and other components. Another application is in the development of co-packaged photonic ICs with electronic ICs. These packages offer a more compact and efficient solution for data transfer between components in computing systems, reducing the need for complex cabling and improving the overall performance and power consumption of the system.

# FOR THE NEXT STAGE IN POWER TESTING

JSUI

0.000 A

0 W

OUTPUT .

+1500

+588 W

NEW

IUltra-compact:20kW in a single 3U size frame.

Maximum voltage:Supports high voltages of 1500V

Bidirectional output: Source and Sink in a single unit!

Increased capacity suitable for testing batteries, inverters, etc.

100% full output, whether the AC input voltage is 200 V or 400 V.

Operating modes\* : CV (constant voltage)/CC (constant current)/ CP(constant power)

\*Priority setting available

Parallel operation up to 10 units(200kW)

Equipped with an intuitive touch panel.

Digital I/O: Customizable control items (5 inputs, 6 outputs)

# **Bidirectional DC Power Supplies** PXB series

https://kikusuiamerica.com kikusui@kikusuiamerica.com Kikusui America, Inc. 3625 Del Amo Blvd, Ste 160 Torrance, CA 90503 Tel: 310-214-0000

# FAQ

: Why is it necessary for me to have a disconnect switch installed in my application? **A:** The main function of a safety disconnect switch is to protect personnel from harm and equipment from damage. Disconnect switches are used to guarantee that a specific electrical circuit is de-energized in the case of an emergency failure, service requirement, or maintenance operation. Disconnect switches have become critical components for electrical distribution systems whether for plantwide use or isolated areas so that technicians can provide repair and maintenance of one machine while the rest of the facility operates normally. In addition, the National Electric Code mandates that disconnect switches are used in all industrial and manufacturing facilities.

# : What does a DC motor disconnect switch do?

**A:** An AC disconnect switch is designed to separate the inverter from the electrical grid, while a DC disconnect switch is designed to separate the equipment from the DC source. Until recently, users had to purchase each of these separately, but companies have created innovative products, like the dual rated disconnect switch that combines both functions for ease of use. The switches must be installed in such a way that incoming power can be quickly shut off whenever an emergency occurs.

: How is it possible that these disconnect switches have evolved to this point?

**A:** A number of factors pull together whenever there is an advancement. Innovation, of course, is an ongoing thing, but other aspects can push technology forward more quickly. For example, as markets change, the availability of materials changes, and the needs of manufacturing change, design teams adjust to meet those situations. At that point, engineers are tasked with not only coming up with new devices to meet present challenges, but to project into the future as well. Only companies with a history in the market have the insights needed to provide this type of innovation.

Could you further discuss some of the technologies used inside these disconnect switches?

> : With the dual rated disconnect switch, do I need additional panel or control room space?

: What specific products are on the market now that meet these challenges?

: Could you supply some technical details concerning these disconnect switches? **A:** High-grade plastics are used to make the switch bodies, which are designed to handle most harsh environments on the factory floor. The tough bodies also operate within a wide temperature range and provide users with a shock resistant and chemical resistant product. Contact quality inside the device was also something the design team focused on. Silver plated contacts and rivets were used throughout the device in order to assure long life and better conductivity.

**A:** Not at all. Technology advancements have added to an engineering team's ability to design products with greater capabilities while maintaining the same form factor. In fact, with smaller areas of real estate being available in such applications as robotics and lab equipment, disconnect switches are often mounted close to the device. This meant that size was a critical factor in the design.

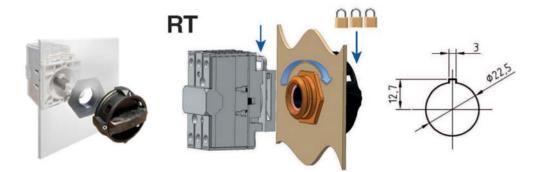

**A:** At this time, Altech has recently introduced the LSF series of disconnect switches that are the only DC switches available in a compact frame size that is dual rated for AC and DC. Due to the needs of the industry, these switches have been made available for mounting in multiple ways, including with an integrated base and DIN-rail mounting, and a separate RT version with integrated door mounting and side panel mounting.

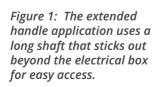

**A:** Basically, the RT devices are provided with rear facing terminals to make them easy to install. For electrical box installations, there are two mounting versions that are dependent strictly on user requirements.

The first option is an extended handle application where the shaft sticks out beyond the electrical box for easy access and interlocks with an external handle so that the box cannot be opened until power is turned off (see Figure 1). Frame size it only 36mm (W) x 71mm (H) x 46mm (D), without integrated switching knob and panel mount tabs.

Sponsored by

Could you supply some technical details concerning these disconnect switches? (continued) The other option is a panel mount version. This disconnect switch is typically installed in a side panel and requires users to drill a small 22.5mm hole into their panel. The hole is used to accommodate the rear-mounted disconnect switch (see Figure 2). Once installed, a knob is attached to the front of the panel for easy access.

*Figure 2: The panel mount option for the LSF series disconnect switch is easy to install.*

Both mounting options have only three parts, unlike most other products on the market that have multiple parts and can be complex to install. The entire LSF series of disconnect switches are available for a wide variety of applications. They are available in 16A, 30A, and 40A versions and offer UL 60947-4-1 certification.

Sponsored by

# Re there any other important design features I need to know about?

**A:** There is another feature that has to do with the switch's make/break operation, which is independent from the operator's turning speed. The actuator arm essentially has nothing to do with changing the switch's state. Internally, the switch is spring loaded so that the DC current cannot arc or burn up the contacts after multiple uses. The switch is turned to a certain point and then snaps into place and cannot be backed off.

# : While incorporating new designs and new technologies, does this affect supply chain deliveries?

A: Great question. When thought through properly, design and automation go hand-in-hand with supply chain considerations. New designs, such as the LSF series, go through rigorous analysis to assure that quality is maintained through the entire line of products being manufactured and that an equal amount of attention is paid to the availability of materials and the reduction of the number of component parts-all aimed at maximizing supply chain capabilities while minimizing the challenges.

Sponsored by

# How to Easily Design **Power Supplies (Part 1)**

This article looks at the LDO and the switch-mode power supply, as well as the most common non-isolated topologies used for SMPS.

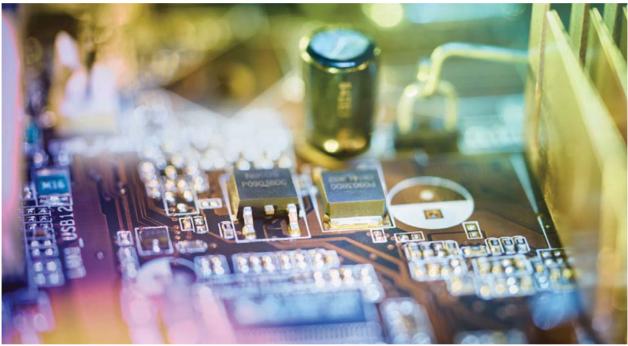

VataBene #1175182921 | iStock / Getty Images Plu

his article series gives an overview of the possibilities for power-supply design. It addresses the basic and commonly used isolated and non-isolated power-supply topologies along with their advantages and disadvantages. Also covered will be electromagnetic interference (EMI) and filtering considerations. This mini tutorial aims to provide a simplified understanding and renewed appreciation for the art of power-supply design.

Most electronic systems require some sort of voltage conversion between the voltage of the energy supply and the voltage of the circuitry that needs to be powered. As batteries lose charge, the voltage will drop. Some dc-dc conversion

can ensure that much more of the stored energy in the battery is used to power the circuitry. Furthermore, for example, with a 110-V ac line, we can't power a semiconductor such as a microcontroller directly.

Since voltage converters, also named power supplies, are used in almost every electronic system, they have been optimized for different purposes over the years. Certainly, some of the usual targets for optimization are solution size, conversion efficiency, EMI, and cost.

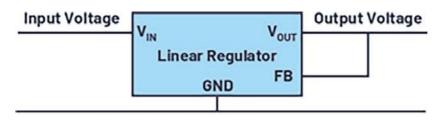

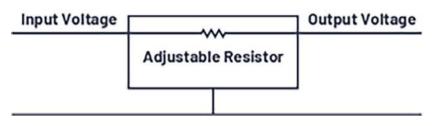

# The Simplest Power Supply: The LDO

One of the simplest forms of a power supply is the low-dropout (LDO) regulator. LDOs are linear regulators as opposed

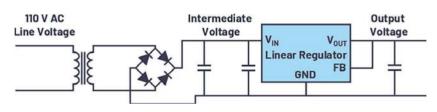

to switching regulators. Linear regulators put a tunable resistor between the input voltage and the output voltage, which means the output voltage is fixed independent of how the input voltage changes and which load current is running through the device. Figure 1 shows the basic principle of this simple voltage converter.

For many years, a typical power converter consisted of a 50- or 60-Hz transformer, connected to the power grid, with a certain windings ratio to generate a non-regulated output voltage-a few volts higher than the needed supply voltage in a system. Then, a linear regulator was used to convert this voltage to a well-regulated one as needed by the electronics. Figure 2 shows the block diagram of this concept. The problem with the basic setup in *Figure 2* is that the 50-/60-Hz transformer is relatively bulky and expensive. Moreover, the linear regulator dissipates quite a lot of heat, so the total system efficiency is low and getting rid of the generated heat is difficult with high system power.

# Switch-Mode Power Supplies to the Rescue

To avoid the disadvantages of a power supply as shown in *Figure 2*, switch-mode power supplies (SMPS) were invented. They don't rely on 50- or 60-Hz ac voltage. SMPS take a dc voltage, sometimes rectified ac voltage, and generate a much higher-frequency ac voltage to use a much smaller transformer. In non-isolated systems, they can rectify the voltage with an LC filter to generate a dc output voltage.

The advantages of SMPS are small solution size and relatively low cost. The ac voltage being generated doesn't need to be a sine voltage waveform. A simple PWM signal shape will work just fine and is easy to generate with a PWM generator and a switch.

Up until the year 2000, bipolar transistors were the most commonly used switches. They would work well but had relatively slow switching transition speed. They weren't very power-efficient, limiting the switching frequency to 50 kHz or maybe 100 kHz.

Today, we use switching MOSFETs instead of bipolar transistors, allowing for much faster switching transitions. This, in turn, gives us lower switching losses, which enables switching frequencies of up to 5 MHz. Such high switching frequencies make it possible to use very small inductors and capacitors in the power stage.

Switching regulators bring many benefits. They generally deliver power-efficient voltage conversion, enable voltage stepup and step-down, and offer relatively compact and low-cost designs. The disadvantages are that they're not so simple to design and optimize, and they generate EMI from the switching transitions and

1. A linear regulator converts one voltage into another.

2. Shown is a line transformer followed by a linear regulator.

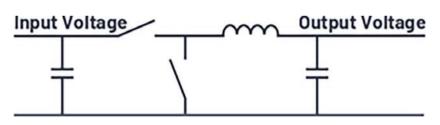

3. Concept of a simple buck step-down converter.

the switching frequency. The availability of SMPS regulators, along with powersupply design tools such as LTpowerCAD and LTspice, have greatly simplified this difficult design process. With such tools, the circuit design process of a SMPS can be semi-automated.

### **Isolation in Power Supplies**

When designing a power supply, the first question should be whether or not galvanic isolation is required. Galvanic isolation is used for multiple reasons. It can make circuits safer; allows for floating system operation; and prevents noisy ground currents from spreading through different electronic devices in one circuitry. The two most common isolated topologies are the flyback and forward converters. However, for higher power, other isolated topologies are employed, such as push-pull, half-bridge, and full-bridge.

If galvanic isolation isn't required, then in most cases a non-isolated topology is used. Isolated topologies always require a transformer, which tends to be expensive, bulky, and often difficult to get off-theshelf with the exact requirements of a custom power supply.

# Most Common Topologies When Isolation Isn't Required

The most common non-isolated SMPS topology is the buck converter. It's also known as the step-down converter. It accepts a positive input voltage and generates an output voltage lower than the input voltage. The buck converter is one of the three most basic SMPS topologies that only require two switches, an inductor, and two capacitors.

*Figure 3* shows the basic principle of the buck-converter topology. The high-side switch pulses a current from the input and generates a switch-node voltage alternating between the input voltage and ground voltage. The LC filter takes that pulsed voltage on the switch node and generates a dc output voltage. Depending on the duty cycle of the PWM signal controlling the high-side switch, a different level of dc output voltage is generated. This dc-dc buck converter is very power efficient, relatively easy to build, and requires few components.

The buck converter pulses current on the input side, while the output side has continuous current coming from the inductor. This is the reason why a buck regulator becomes very noisy on the input side and not so noisy on the output side. Understanding this is important when low-noise systems must be designed.

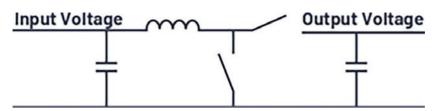

# Boost

Besides the buck topology, the second basic topology is the boost, or step-up, topology (*Fig. 4*). It uses the same five basic power components as the buck converter, but rearranged, so that the inductor is placed on the input side and the high-side switch is placed on the output side. The boost topology is used to step up a certain input voltage to an output voltage that's higher than the input voltage.

4. Concept of a simple boost step-up converter.

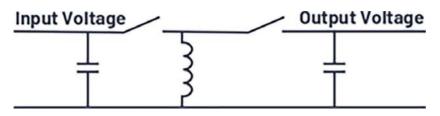

5. Concept of a simple inverting buck-boost converter.

When selecting a boost converter, it's important to note that boost converters always specify the maximum rated switch current and not the maximum output current in their datasheets. In a buck converter, the maximum switch current is directly related to the maximum achievable output current, independent of voltage ratio between the input and output voltage. In a boost regulator, the voltage ratio directly affects the possible maximum output current based on a fixed maximum switch current. When selecting a suitable boost regulator IC, you need to not only know the desired output current, but also the input and output voltage of the design in development.

A boost converter is very low noise on the input side because the inductor in line with the input connection prevents rapid changes in current flow. However, on the output side, this topology is quite noisy. We only see pulsed current flow through the outside switch, and thus output ripple is more of a concern compared to the buck topology.

### **Buck-Boost**

The third basic topology, only consisting of the five basic components, is the inverting buck-boost converter (*Fig. 5*). The name is derived from the fact that this converter takes a positive input voltage and converts it into a negative output voltage. Besides this, the input voltage may be higher or lower than the absolute of the inverted output voltage. For example, -12 V output voltage may be generated out of 5 V or 24 V on the input. This is possible without making any special circuit modifications.

In the inverting buck-boost topology, the inductor is connected from the switch node to ground. The input side as well as the output side of the converter see pulsed current flow, making the topology relatively noisy on both sides. In low-noise applications, this nature is compensated by adding additional input and output filtering.

One quite positive aspect of the inverting buck-boost topology is the fact that any buck switching-regulator IC may be used for such a converter. It's as simple as attaching the output voltage of the buck circuit to system ground. The buck IC circuit ground will become the adjusted negative voltage. This trait leads to a very large selection of switching-regulator ICs on the market.

**TO READ** Parts 2 and 3, or to download an eBook of the entire series, go to https:// electronicdesign.com/21265533.

പ്പ

SMART DATA-AI

SMART MOBILITY ഄ൳ഀഁ

SMART MEDTECH

Connecting Semiconductors and **Electronics**

Global

ADVOCACY

WORKFORCE DEVELOPMENT

Sustainability

# About SEMI:

SEMI connects more than 2,500 member companies and 1.3 million professionals worldwide to advance the technology and business of electronics design and manufacturing. The breadth and depth of our events, programs and services help members accelerate innovation and collaboration on the toughest challenges to growth.

1000+ STANDARDS

THOUGHT LEADERSHIP

# SEMICON

TECH COMMUNITIES

SEMI UNIVERSITY

Cyber Security

# Why are Specifications and Characterizations for Op Amps and FDAs Different and Confusing?

From input offset voltage to slew rate to gain bandwidth product, specifications for operational amplifiers can vary widely amongst different vendors.

t can be a maddening (and time-consuming) task to compare data across vendors to get a real comparison between possible solutions. Between "marketesse" and just plain deception and/ or errors, how can you see through these and normalize critical specs across vendors to get real comparisons.

Having contributed to the development and product launch of over 150 high-speed amplifiers from 1985 forward, the level of detail and tradeoffs going into product datasheets and simulation models probably exceeds the wildest imaginings of the end-system designers. Here you will learn some of the hidden background for (and often confusing) specifications along with what to look out for in characterization curves and vendor simulation models.

First, who does this work and what do they bring to the task?

# IC design engineer

The designer, working with the latest process design kit (PDK) takes the marketers end-product targets and iterates over many months to get close. Usually, these targets take the form of more and more performance at lower and lower supply current.

Occasionally, a new topology will come along that fills an important niche, such as

the fully differential amplifier (FDA) and current feedback amplifier (CFA). Once the nominal transistor-level topology is set, he/she will start running statistical process case and over-temp simulations to extract out corner cases for the proposed end limits on key specs. PDKs have evolved to be remarkably good; only some of that gets into the datasheet and customer simulation models.

# Marketing engineer

Looking at the extant solution universe, the marketing engineer tries to carve out unique and valuable new product targets. Through the course of design and introduction, he/she trades off "don't care" versus "must care" specs with the designer to hopefully emerge with a meaningful new solution for the analog design community.

# ATE engineer

This key team member is tasked with layering over a set of probe and/or finished product tests to ensure nothing ships that's defective. In the early days of high-speed amplifiers, 100% ac testing was done at Comlinear Corp on the industry's first current feedback op amps using an HP3577 network analyzer. Over time, it became clear that a full suite of stressful dc tests shipped good ac parts and that production expense was eliminated.

With a few exceptions, all current precision and higher-speed amplifiers receive only a dc test at probe and/or final test at some nominal temperature (with some span on that), imputing ac performance within the designer worstcase simulation results.

The ATE engineer is incentivized to deliver tests and limits with 100% yield. The marketing engineer must resist this—say, on input offset voltage, a  $\pm 3.5$ -sigma test limit is probably adequate (implying no more than 0.04% yield loss). Expanding single-lot ATE data to final datasheet limits is largely internal culture, designer simulation tools, and judgement calls among the development team members and any QA mandates that might be imposed.

# Applications engineer

Directed by the marketing engineer, and with an assist from design, the application engineer is tasked with taking the characterization curves and working with the modeling team to develop and test the public simulation model. This is where the rubber meets the road in what the customer sees as a product support package. He/she will also add suitable application text and examples to the final datasheet to illustrate the fabulous new capability for a device that probably cost well over \$1M to develop.

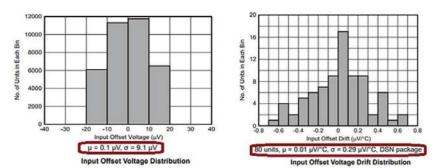

1. Recent OPA2863A offset and offset drift histogram examples show widely different plus/ minus sigma limits.

# Personnel and Datasheet "Churn"

One of the difficulties with consistent and accurate material is the relative turnover in these positions. Often, the designer and ATE engineer are 20-plus-year folks. There's quite a bit of churn in the marketing and applications roles where the latter might be just out of school. Hence, a very tenuous thread links today's datasheets to those done even 10 years ago (and nearly none to those done 20 years ago).

At a more basic level, no NIST reference document exists on how the different specs and characterization curves "must" be done. In fact, on some of the critical specs, there's been an ongoing evolution of better methods.

For instance, when I first started doing distortion plots (circa 1987), about -90 dBc was the measurement limit imposed by spectrum analyzers. Today, bench techniques reach down near -150 dBc (if you want to spend enough effort on it, very non-trivial—operating above audio precision measurement frequency range).

# Clarifications on Occasionally Murky DC Specs

Most of the op-amp and FDA dc specifications are pretty clear. Some, but not all, of the dc specifications become the final test lines. A few can cause confusion at times, particularly those with a zero mean as well as the output current specification.

# Input offset voltage

The input offset voltage (and current for bipolar inputs) will usually have a distribution centered on zero. Modern devices trim this to a zero mean at either wafer probe or packaged eTrim. So what do you specify for a typical, because "0" doesn't really give you much information?

The informal practice across the industry is to report the  $\pm 1$ -sigma number as the typical specification to avoid customer surprises when devices with a zero mean don't test at zero for typical devices. Specifications for a maximum input offset voltage (and current where needed) are extremely inconsistent. Essentially those are a combination of a plus/minus shift of the mean off of zero plus/minus some number of standard deviations.

My practice was to impose a  $\pm 3.5$ -sigma range (THS4551) to accept approximately 0.04% yield loss. Other devices and product groups allow for much wider limits (OPA837, THP210, ADA4805, etc). Some of this is related to test repeatability, where there's also an error band in test over different physical testers. While this might pass more units, you do wonder if devices way out on the distribution tails (some allow for >8 sigma) might be shipping "defective" units.

These same issues apply to the specified input-offset-voltage temperature drift, where it's extremely rare to see this as a 100% tested specification (the JFET input OPA656 is one of the very few). Maximum offset drift numbers are sometimes provided without ATE screens (OPA2683A, ADA4895), while many more devices have no maximum drift spec(s).

The guaranteed maximum drift numbers are from extensive bench characterization of packaged units that are (hopefully?) at the extreme allowed limits of the tested room-temp input offset voltage (and current where appropriate). Drift magnitude is often linearly related to initial offset, so testing units at the allowed limit should expose the worstcase drift specs.

Figure 1 shows a recent example where the tested  $V_{os}$  limits are ±95  $\mu$ V (or ±10 sigma), imputing a drift limit of ±1.2  $\mu$ V/°C or ±4 sigma. The actual  $V_{os}$  histogram data in *Figure 1* is much tighter than the ATE limit in the specification table. Apparently, the ATE engineer got this through while the marketer was out traveling.

# **Output current**

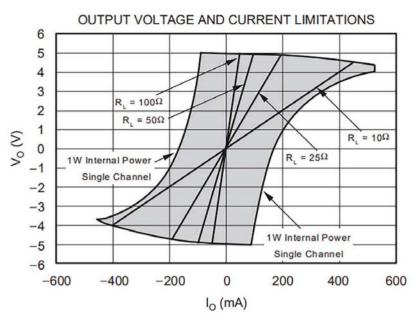

Probably the most slippery dc specification on any op-amp or FDA datasheet is the output current. Marketers want the biggest number possible. Designers struggle with that as large output devices bring an increased capacitance, which adds open-loop phase shift that impairs achievable bandwidth on ever-declining supply current budgets. ATE engineers are all over the map in how this might be tested.

Physically, the output-current demand will get involved with the available "linear" output-voltage swing available. Every device (even rail-to-rail outputs) will see an increase in required headroom to the supplies for linear operation due to rising load-current demand. Keep in mind that not only the actual load, but also the feedback network, is part of that load. In non-inverting configurations, that's the sum of the feedback and gain resistors, while in inverting configurations (and for FDAs), it's just the feedback resistor appearing in parallel with the actual load.

First, it's important to recognize that any "short circuit" current specification

2. Shown is an example four-quadrant output VI limit for a dual CFA high-power PLC line driver.

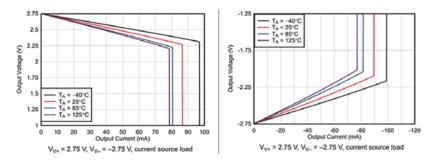

3. Compared are the output swing vs. current for the RRIO precision OPA328.

is usually a self-limited (base or gate drive) typical specification. Traditionally, it needs to be there, but it doesn't really give you much information. Only when there is a min. or max. specification is there an "active" current limit in the output stage design (THS3491), with some exceptions (OPA2683A).

Over time, several different efforts at a "linear" output-current specification have been attempted. During the PLC line-driver developments (where the line can push current back into an amplifier output), a four-quadrant envelope of limits was shown—like that in *Figure 2* taken from the OPA2674 datasheet (on  $\pm$ 6-V supplies). Only the quadrants with the load lines describe normal operation here.

More typically, a bipolar "claw" curve has evolved to describe the loss of output headroom, as more sourcing or sinking current is required. Here, the two polarities are separated into two plots, but the increase in required headroom with out-

| Maximum current into a resistive load | $T_A \approx 25^{\circ}$ C, ±1.6 V into 27 Ω, V <sub>IO</sub> < 2 mV                               | ±58 | ±70 | mA | А |

|---------------------------------------|----------------------------------------------------------------------------------------------------|-----|-----|----|---|

| Linear current into a resistive load  | $T_{A} \approx 25^{\circ}\text{C},  \pm 1.7 \text{ V}$ into 37.4 $\Omega,  A_{OL} > 80 \text{ dB}$ | ±45 | ±50 | mA | Α |

4. This is an example linearity test for output current and voltage into a resistive load for the OPA837.

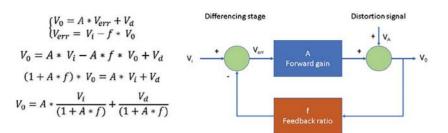

put source/sink current is clearly shown in *Figure 3*.