# Electronic Design.

- C C

**í**Oľ

Volume 2

H

Vol. 2, No. 1

### Generate Realistic Models For LED Current Versus Voltage

Designers of lighting drivers require a good approach to modeling LED device performance in the first quadrant of the I/V plane. For engineering applications, there are three approaches to consider: the linear, bias-voltage plus resistor equivalent, a quadratic equation, and an exponential equation.

#### PWM-Based Analog Calculator Provides Four-Quadrant Multiplication, Division

You can build an analog calculator using a pulse-width modulator (PWM) to perform accurate four-quadrant multiplication and division. While this approach won't help you ace any math tests, it demonstrates some useful sub-circuits that extend the functionality of the LTC6992 TimerBloxvoltage-controlled PWM.

#### Driven Shield Enables Large-Area Capacitive Sensor

This low-cost, large-area capacitive sensor is the wide-scale complement to the ubiquitous, finger-operated touchscreen sensor and can detect presence through plywood or wallboard.

Do you have an Idea for Design for Electronic Design? *Electronic Design* is always on the lookout for new ideas. Do you have one? Our Ideas for Design articles are short and to the point, often with a single figure or program listing to help explain the idea. If you would like to submit one, you can check out the details at

<u>https://www.electronicdesign.com/contribute.</u> We look forward to seeing your ideas.

KENG C.WU | SWITCHING POWER INC., kengchi.goah@ieee.org

# **Generate Realistic Models For LED Current Versus Voltage**

LEDS ARE NONLINEAR devices with I/V curves that resemble the THE QUADRATIC MODEL curves of rectifier diodes. Designers of lighting drivers require a good approach to modeling the LED device performance in the first quadrant of the I/V plane.

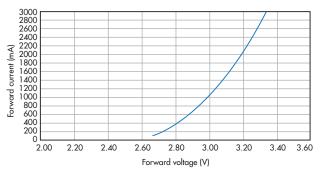

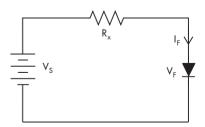

For engineering applications, there are three approaches to consider: the linear, bias-voltage plus resistor equivalent; a quadratic equation; and an exponential equation. Let's use the three techniques with Cree's XLamp XM-L LED as the LED to be modeled (Fig. 1).

#### THE LINEAR MODEL

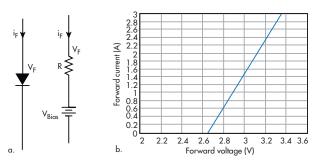

This model is the simplest, but the most inaccurate. It consists of a dc bias voltage plus a resistor (Fig. 2a). The equivalent mathematical form is given by:

$$i_F(v_F) = a + \frac{1}{R}(v_F - b) = \frac{v_F - v_{bias}}{R}, \quad v_F \ge v_{bias} = b - a \cdot R \quad (1)$$

You select two data points  $(v_F, i_F)$  in coordinate form (i.e., 3.28 V, 2.6 A and 2.71 V, 0.2 A). Then, R is evaluated and yields 0.2375. The selection also implies a = 0.2 and b = 2.71. With all three parameters (a, b, R) properly assigned, the linear model yields Figure 2b. Evidently, the linear model offers the advantage of simplicity, but suffers in accuracy.

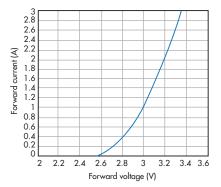

The curve of Figure 1 has a concave portion that resembles one arm of a parabolic curve. It can be expressed with a quadratic equation of the form  $a_2v_F^2 + a_1v_F + a_0$ . The key is the determination of three coefficients: a2, a1, and a0.

To determine these coefficients, you can use the well-known Least Square Polynomial Curve-fitting algorithm of linear algebra. To do this, select more than a dozen data points from Figure 1 (15 in this case) and place them in two matrixes.

One is a 3x15 rectangular matrix C (Equation 2). The other is a 1x15 column vector  $i_F$  (Equation 3) where  $vF_i$ , for j = 0 to 14, are the corresponding LED forward voltages at the selected forward currents given in vector i<sub>F</sub>. The three coefficients are then given by a column vector of:

$$\mathbf{a} = (\mathbf{C} \cdot \mathbf{C}^{\mathrm{T}})^{-1} \mathbf{C} \cdot \mathbf{i}_{\mathrm{F}}^{\mathrm{T}} \quad (4)$$

Using software tools such as Matlab from the Mathworks or MathCAD from Mathsoft, you can easily compute Equation 4. For this example, we obtain:

$$a = \begin{pmatrix} 24.849\\ -20.093\\ 4.058 \end{pmatrix}$$

(5)

200m 400m 600m 800m 1000m 1200m 1400m 1600m 1800m 2000m 2200m 2400m 2600m 2800m 3000m (3) iF :=

1. Modeling the I/V curve of the Cree XLamp XM-L LED with increasing accuracy is the objective of this analysis.

2. The linear model (terminal view) is simplest and easiest to understand, but also the least accurate (a). The linear model results in this "curve," which clearly has some shortcomings (b)

Note that the first element of vector a is coefficient  $a_0$ , etc., which leads to the quadratic model of Figure 3. This approach yields significant improvements in the model across the whole operating range of the LED.

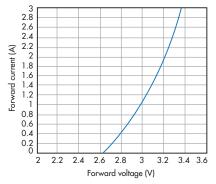

#### THE EXPONENTIAL MODEL

Figure 3 appears to bend more near the low current, which is where the exponential model may offer further improvement. This model comes in the form of  $ae^{b\cdot vF} + c$  with three unknown parameters a, b, and c to be determined. Again, software tools such as MathCAD help you find those parameters numerically.

Under the specialized regression section, an exponential regression statement expfit ( $v_F$ ,  $i_F$ , vg) can find all three parameters, given a data set in vectors and initial guess value vg, also a column vector. For this example, a =  $9.66 \cdot 10^{-3}$ , b = 1.818, and c = -1.157 are obtained. This results in the exponential model of Figure 4.

3. The curve based on a quadratic model curve is much closer to the reality of the I/V curve for this LED.

Overall, the best fit near the low-current region may be found between the quadratic and the exponential models. It is unrealistic to expect a single, perfect

4. The exponential model further refines the quadratic model and provides a better approximation in the low-current region of the LED.

prediction from any given model, since almost all such analytical efforts are an attempt to represent the complexities of nature.

KENG C. WU has a BS from Chiaotung University, Taiwan, and an MS from Northwestern University, Evanston, III. He has published four books and holds seven U.S. patents.

MARK THOREN | LINEAR TECHNOLOGY CORP. mthoren@linear.com

# **PWM-Based Analog Calculator Provides** Four-Quadrant Multiplication, Division

**YOU CAN BUILD** an analog calculator using a pulse-width modulator (PWM) to perform accurate four-quadrant multiplication and division. While this approach won't help you ace any math tests, it demonstrates some useful subcircuits that extend the functionality of the LTC6992 TimerBlox voltagecontrolled PWM.

The LTC6992-1 translates a 0-1 V input at the MOD pin into an output with a 0% to 100% duty cycle at a frequency of 3.81 Hz to 1 MHz. A resistor at the SET pin and a resistor divider at the DIV pin control this frequency. In some applications, the LTC6992 will be in the feed-forward path of a closed-loop control system (as in a motor-speed controller), so its 1% typical linearity provides consistent overall loop performance.

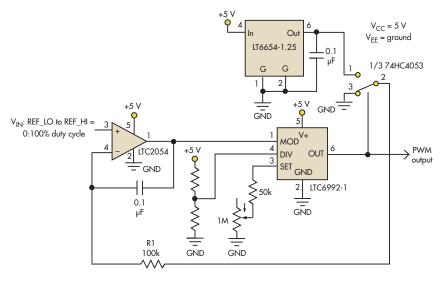

Figure 1 shows a basic linearized a PWM generator for applications where

accurate PWM is required without an external feedback mechanism. This circuit easily achieves 0.1% PWM accuracy. The output of the LTC6992 controls one section of a 74HC4053 triple single-pole double-throw (SPDT) analog switch whose output is switched between ground and an LT6654-1.25 reference. An integrator compares this signal to the control input. The output duty cycle will settle on a value that equals the fraction of the 1.25-V reference that's present at the input. The term "fraction" implies that this circuit performs division, as the output PWM duty cycle is V<sub>In</sub>/V<sub>Ref</sub>.

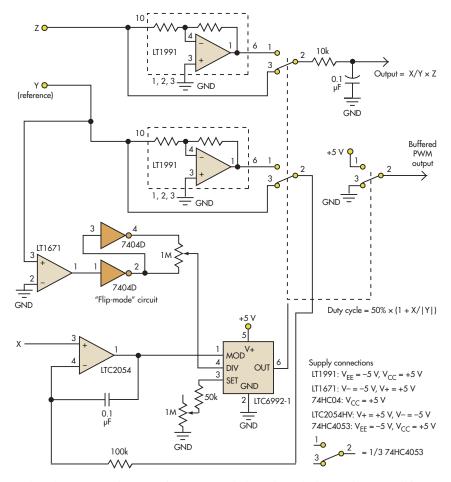

Figure 2 extends this concept, with X as the input (numerator) and Y as the reference (denominator). An LT1991 configured in a gain of -1 provides a precise negative copy of Y, extending operation to four quadrants (positive and negative X and Y), with duty cycle =  $50\% \times [1 + (X/|Y|)]$ .

As with any physical realization of division, a zero value for the denominator (Y) will produce an undefined output. A negative voltage applied to the Y input inverts the polarity of the feedback signal to the integrator, which requires another inversion

1. This basic linearized PWM generator, without an external feedback mechanism, can still provide accuracy of 0.1%.

|         | DIVCODE PROGRAMMING |                  |                              |         |         |  |  |  |  |

|---------|---------------------|------------------|------------------------------|---------|---------|--|--|--|--|

| DIVCODE | POL                 | N <sub>DIV</sub> | Recommended f <sub>Out</sub> | R1 (kΩ) | R2 (kΩ) |  |  |  |  |

| 0       | 0                   | 1                | 62.5 kHz to 1 MHz            | Open    | Short   |  |  |  |  |

| 1       | 0                   | 4                | 15.63 to 250 kHz             | 976     | 102     |  |  |  |  |

| 2       | 0                   | 16               | 3.906 to 62.5 kHz            | 976     | 182     |  |  |  |  |

| 3       | 0                   | 64               | 976.6 Hz to 15.63 kHz        | 1000    | 280     |  |  |  |  |

| 4       | 0                   | 256              | 244.1 Hz to 3.906 kHz        | 1000    | 392     |  |  |  |  |

| 5       | 0                   | 1024             | 61.04 to 976.6 Hz            | 1000    | 523     |  |  |  |  |

| 6       | 0                   | 4096             | 15.26 to 244.1 Hz            | 1000    | 681     |  |  |  |  |

| 7       | 0                   | 16384            | 3.815 to 61.04 Hz            | 1000    | 887     |  |  |  |  |

| 8       | 1                   | 16384            | 3.815 to 61.04 Hz            | 887     | 1000    |  |  |  |  |

| 9       | 1                   | 4096             | 15.26 to 244.1 Hz            | 681     | 1000    |  |  |  |  |

| 10      | 1                   | 1024             | 61.04 to 976.6 Hz            | 523     | 1000    |  |  |  |  |

| 11      | 1                   | 256              | 244.1 Hz to 3.906 kHz        | 392     | 1000    |  |  |  |  |

| 12      | 1                   | 64               | 976.6 Hz to 15.63 kHz        | 280     | 1000    |  |  |  |  |

| 13      | 1                   | 16               | 3.906 to 62.5 kHz            | 182     | 976     |  |  |  |  |

| 14      | 1                   | 4                | 15.63 to 250 kHz             | 102     | 976     |  |  |  |  |

| 15      | 1                   | 1                | 62.5 kHz to 1 MHz            | Short   | Open    |  |  |  |  |

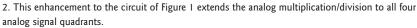

3. This plot of absolute error shows better than 0.1% for large values of Y.

somewhere in the loop to ensure feedback is negative.

The DIV pin also can invert the PWM polarity (a 0- to 1-V input = 100% to 0% duty-cycle output), in addition to selecting one of eight  $N_{Div}$  values to set the frequency. The  $N_{Div}$  magnitudes are mirrored around  $V_{CC}/2$ , where swapping values in the resistor divider inverts the transfer function while maintaining the same divider value (see the table).

An LT1671 comparator detects the polarity of the Y input and sets the polarity by switching the divider potentiometer's excitation accordingly, maintaining correct operation. Note that a 10-turn potentiometer works well for experimentation. You could replace it with a fixed resistor once you have selected the desired N<sub>Div</sub>.

The "Z" input is multiplied by the X/Y quotient by supplying the inputs to another switch with Z and –Z. (Once again, an LT1991 provides precision inversion.) This is a "pulse width/pulse height" multiplier, also with four-quadrant operation.

Figure 3 shows the absolute error of the circuit at a 1.5-kHz frequency, sweeping X from -Y to +Y for values of Y from -3 V to +3 V, while holding Z constant at 5 V. Even with Y at 0.5 V (where error sources are more significant), the worst-case error is about 0.6% and rapidly improves with larger values of Y. Error sources include the 0.04% error of the LT1991, mismatch in switch resistance between its two positions compared with the resistance of the downstream filter's resistance, and the response of the LT1991 outputs to switching transients, whose effect will vary with PWM frequency.

MARK THOREN is the applications engineering manager for mixed-signal products at Linear Technology. He has a BS in agricultural/mechanical engineering and an

MS in electrical engineering, both from the University of Maine.

## Driven Shield Enables Large-Area Capacitive Sensor

**CAPACITIVE SENSORS ARE** common in today's consumer electronics, since they are used in many touchscreen applications. Most of the circuits for such applications are designed for small-area capacitors and finger contact operation.

This circuit is designed for large-area touch plates that can be activated at a distance and hidden behind walls or inside other structures. It uses the "driven shield" concept that was popular in the early days of audio engineering, when high-impedance sound sources such as crystal microphones were used. Shielded cables are needed to connect these devices, but the cable capacitance limits the high-frequency response.

The solution to this problem is to go back to the physics of a capacitor to find a way to reduce the cable capacitance. Driving a conductor between the

outer shield and the inner, signal conductor with the same voltage as the signal conductor largely eliminates the capacitance. NASA used this driven-shield idea in a large-area capacitive sensor two decades ago (John M. Vranish, et al., US Patent No. 5,116,679).

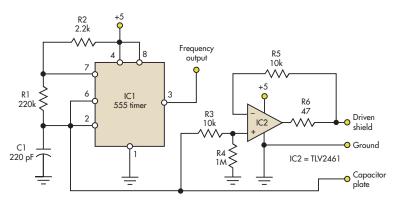

The circuit in Figure 1 performs the main capacitancesensing task, while leaving detection to a microcontroller. IC1 is a 555 timer wired as an astable multivibrator with as small a timing capacitance as possible. With the component values shown, the frequency is slightly above 10 kHz. IC2 buffers the voltage on this capacitor to drive a shield plate.

For IC2, resistors R3 and R4 decrease the buffered voltage by about 1%. This prevents oscillation that may occur because of the external capacitance. R6 is included since some operational amplifiers have difficulty driving a capacitive load. IC2

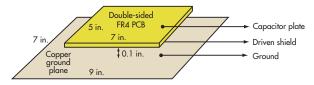

2. In the constructed sensor, a double-sided printed-circuit board (PCB) has one conductor as the signal plate and the other as the driven shield. The semi-infinite ground plane, which is slightly larger in area than the sensing or shield plates, can be another PCB or an aluminum plate.

DEV GUALTIERI received his PhD in solid-state science from Syracuse University in 1974. He now does various computer, electronic, and embedded systems projects at his consulting company, Tikalon LLC.

1. In this large-area capacitive sensor, C1 and any parallel capacitance set the frequency of the 555 astable multivibrator IC1, while IC2 buffers the voltage at the capacitor to drive the shield plate. (The pin-outs for IC1 are for the "N" package.)

should have a high gain-bandwidth product to allow a faithful representation of the signal voltage without phase shift.

Figure 2 shows the construction of the sensing plate. These are the dimensions used in the author's tests, but quite a lot of variation is permissible. A practical implementation would be to build the circuitry onto an edge of the ground plane.

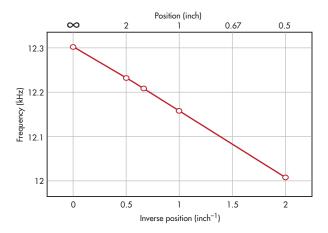

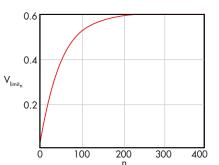

The frequency response decreases in a nearly linear fashion with respect to inverse position (*Fig. 3*). In the author's test, hand contact reduced the frequency to 10.47 kHz. Hand contact through a 0.375-in. (10 mm) thick piece of plywood or gypsum wallboard resulted in a frequency change of 10%, which is easy to detect. Although frequency-detection ICs are available, a simpler, less expensive solution is to use a microcontroller to detect a change in signal period.

3. The circuit response is a close-to-linear inverse-position relationship between hand position and the sensing plate.

Vol. 2, No. 2

#### Test Setup Checks Transistors' h<sub>FE</sub>s When Tight Control Is Important

This circuit uses pulsed current to check transistor hFE on an oscilloscope. The circuit creates the biasing conditions specified by the transistor's manufacturer..

#### Multiple Power Supplies Fortify High-Side Gate Control

A switching power supply was devised to ensure high-side FET gate control, particularly in light of a wildly floating high-side rail. The design's "VeeDrive" delivers a sharp and muscular square-wave that's robust enough to drive several charge pumps.

#### High-Side Switch Provides Overvoltage Protection With Only Four Components

Low-voltage microcontrollers often need to control higher-voltage loads via high-side switching. This simple two-transistor circuit enables that control and provides over-voltage protection.

#### Add Short-Circuit Protection, Diagnostics To Automotive High-Side/Low-Side Driver

Smart switches for automotive applications are costly, may not be readily available for 24-V operation, and often come in unneeded dual and quad configurations. By adding a few standard, low-cost components to a basic driver, you can make a smarter one which includes short-circuit protection and built-in diagnostics.

Do you have an Idea for Design for *Electronic Design*? *Electronic Design* is always on the lookout for new ideas. Do you have one? Our Ideas for Design articles are short and to the point, often with a single figure or program listing to help explain the idea. If you would like to submit one, you can check out the details at

<u>https://www.electronicdesign.com/contribute.</u> We look forward to seeing your ideas.

#### CHEE HUA HOW | TDK MALAYSIA cheehhow@yahoo.com

## Test Setup Checks Transistors' h<sub>fe</sub>s When Tight Control Is Important

**THE SPREAD OF**  $h_{FE}$  values in a batch of bench evaluation of  $h_{FE}$  may be required transistors may be wide enough to cause during the system's development stage. unreliable performance during mass Designers may have to screen samples production of a system. Consequently, over a spread of several years of date

codes. Sometimes these measurements are made using pulsed collector current.

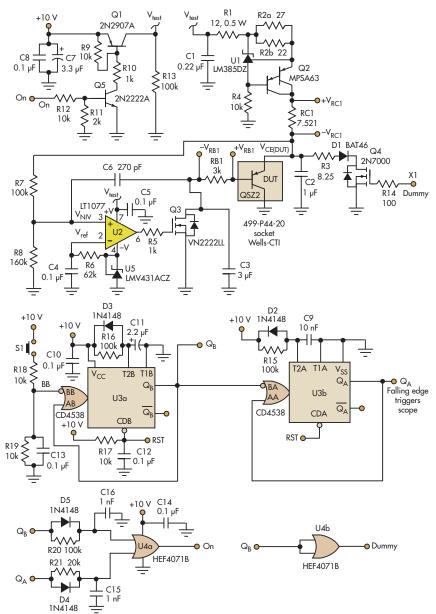

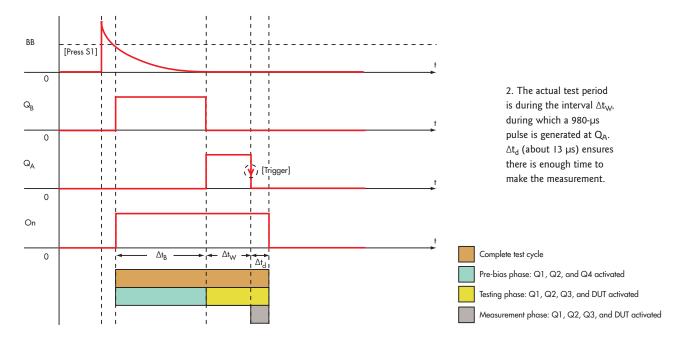

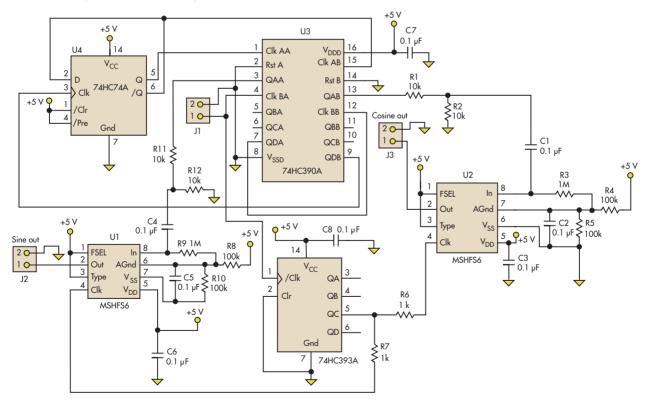

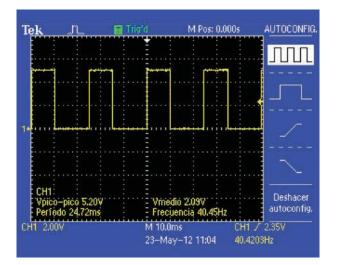

This idea describes how to make such measurements. For example, the QSZ2 transistor (2SB1695) specification states three biasing requirements on  $h_{FE}$ :  $I_C =$ 0.1 A,  $V_{CE} = 2$  V, and  $\Delta t_w = 1$  ms. The circuit in Figure 1 meets these requirements for h<sub>FE</sub> measurement for a QSZ2 pnp transistor.

Zener U1 and its associated components form a current regulator that sources 0.1 A to the succeeding stage. During the test period ( $\Delta t_W$  in Figure 2), U2's feedback mechanism trims the base resistance of the device under test (DUT) while maintaining its V<sub>CE</sub> at the required 2 V. This is expressed in Equation 1, in which R<sub>DSO3</sub> is automatically tuned against IB(DUT) and, therefore,  $h_{FE}$  and  $V_{BE(DUT)}$  variations:

$$V_{CE(DUT)} = V_{BE(DUT)} + V_{RB1} + V_{DSQ3}$$

= 2 V

$$V_{BE(DUT)} + I_{B(DUT)} (R_{B1} + R_{DSQ3})$$

= 2 V

(1)

Equation 2 then allows you to determine the value of the DUT's h<sub>FE</sub> by monitoring V<sub>RB1</sub>:

$$\frac{I_E}{I_B} = (h_{FE} + 1) \approx h_{FE} \text{ if } h_{FE} \gg 1$$

$$h_{FE} = \frac{0.1 \text{ A}}{\frac{V_{RB1}}{3 \times 10^3}} = \frac{300}{V_{RB1}}$$

(2)

Basically, resistor RB1's value is set as large as possible to minimize the oscillation of IB(DUT) upon transition and to

1. This test circuit provides the biasing conditions needed to evaluate a transistor's hFF according to the manufacturer's criteria. In this example, the device under test is a QSZ2 (2SB1695), and the values chosen are specific to that device.

maximize the signal level to ease  $V_{RB1}$  monitoring. The h<sub>FE</sub> of a QSZ2 ranges from 270 to 680, so  $I_{B(DUT)}$  falls between 147  $\mu$ A and 370  $\mu$ A.

Next, assume the worst-case  $V_{BE(DUT)}$  variation of 0.5 V to 0.8 V. Then:

$$R_{B(min)} = \frac{\left(V_{CE(DUT)} - V_{BE(max)}\right)}{L} = \frac{\left(2 - 0.8\right)}{370 \text{ µA}} = 3.243 \text{ k}\Omega \quad (3)$$

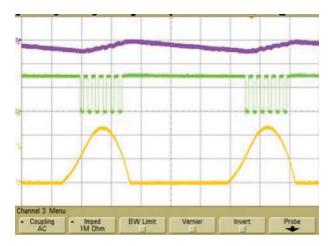

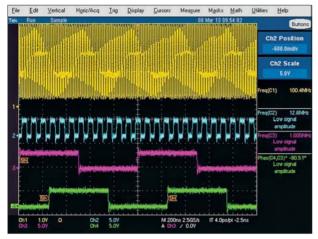

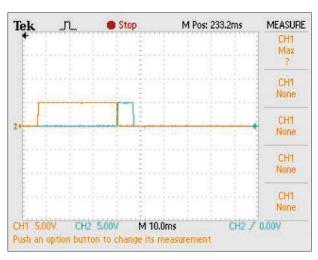

3. The falling edge of  $Q_A$  triggers an oscilloscope, which uses  $V_{RB1}$  (trace A) and  $V_{RC1}$  (trace B) to calculate  $h_{FE}$  (trace D).

$$R_{B(max)} = \frac{\left(V_{CE(DUT)} - V_{BE(min)}\right)}{I_{B(min)}} = \frac{\left(2 - 0.5\right)}{147 \ \mu A} = 10.204 \ k\Omega$$

(4)

Choose RB1 so that it is slightly below R<sub>B(min)</sub>.

The circuitry around U3 forms two cascading one shots that, when triggered by S1, generate a 220-ms pulse ( $\Delta t_B \approx R16 \times C11$ ) at the Q<sub>B</sub> output. This is followed by a 980-µs pulse,  $\Delta t_W$ (determined by R15 and C9), at Q<sub>A</sub>. The first pulse pre-biases and stabilizes the current source while the second one provides the needed test pulse for the DUT.

During  $\Delta_{tB}$ ,  $Q_4$  is activated to sink the 0.1 A of U1, and R3 is selected so the effective voltage drop across R3, D1, and Q4 (and thus  $V_{CE(DUT)}$ ) is slightly less than 2 V (about 1.7 V in this example). This forces U2's output and the DUT to stay "low" and "off," respectively.

At the end of  $\Delta t_B$ ,  $\Delta t_W$  starts and Q4 is turned off, transferring the test current to the DUT. U2 then raises  $V_{CE(DUT)}$  to 2 V and regulates it.

The high-to-low transition at the  $Q_A$  output after  $\Delta t_W$  triggers the measuring device (in our example an oscilloscope) (*Fig. 3*).  $V_{RC1}$  and  $V_{RB1}$ , which correspond to  $I_C$  and  $I_B$  of the DUT, are recorded upon  $Q_A$ 's trigger. R21 and C15 create  $\Delta t_d$  (about 13 µs), which ensures enough time to make the measurement before Q1 is gated "off."

For more, see "Anoop's Analysis" with the online version of this article at electronicdesign.com.

CHEE HUA HOW, design engineer, specializes in analog and power electronics design. He has an MSEE from Multimedia University, Malaysia, and a BSEE from Coventry, University, the U.K.

# Multiple Power Supplies Fortify High-Side Gate Control

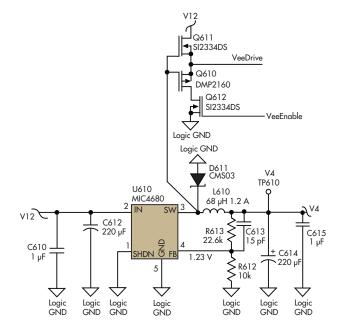

**FOR A RECENT** design project, a robust power supply was needed to control the gates of high-side FETs. Optocouplers readily translate the logic signals up to the correct control voltages to drive the FETs. However, to ensure that the FETs turn on and off cleanly, the design required a solid -15 V relative to a wildly floating high-side rail.

A simple Zener diode and resistor, possibly with a FET buffer to ensure adequate current, might do the job under some conditions. In certain circumstances, though, the required gate drive would dip slightly below the lowest other supply rail in the system, which is in this case GND, since there are no negative supplies. At other times, it could be almost 100 V above all other supply voltages. Since the design in question was to be used in a production scheme, the solution had to stay away from proprietary, expensive, single-source parts.

The design already included a switching supply to efficiently convert from an incoming supply at approximately 12 V, down to an internal logic supply at 4 V (*Fig. 1*). The switch node of that supply, at the junction of U610 pin 3, L610, and D611, swings between the incoming 12-V rail and a diode drop below ground—approximately -0.5 V. This could provide the feed for a charge pump. However, the 4-V supply can't be lightly loaded, which would cause insufficient drive at this point to support a charge pump.

To guarantee a solid drive for the charge pump, power is derived directly from the 12-V supply and ground using transistors Q610 and Q611. Note that these aren't configured in a traditional inverter configuration, which could suffer from shoot-through when both are turned on simultaneously during the gate's voltage transition.

Instead, transistors Q610 and Q611 are simple source-followers. As the gate voltage rises more than about a volt above the present value of net VeeDrive shown in Figure 1 at the source terminals of Q610 and Q611, Q611 turns on, pulling up VeeDrive so it remains about 1 V below the gate voltage all the way up. On the falling edge at the switch node, the gate voltage falls, Q611 is turned solidly off, and Q610 begins to turn on as the gate voltage falls about 1 V below VeeDrive. Therefore, VeeDrive follows the gate voltage down to within about 1 V of Logic GND.

As a result, VeeDrive provides a sharp and muscular squarewave that swings between about 1 V and 11 V (relative to Logic GND), for a total of 10 V p-p. It's robust enough to drive several charge pumps, if the need arises for multiple supplies. In fact, this one square-wave provided all four supplies required by the design at hand.

Q612 is an optional component. Raising net VeeEnable, the gate drive to Q612, to a logic high voltage turns on Q612 and enables the charge pump action. Lowering VeeEnable back to

Logic GND turns off Q612 and disables the low-side drive, allowing VeeDrive to settle to a steady state just below V12. This will save power during those times that don't require the GateDrive supply.

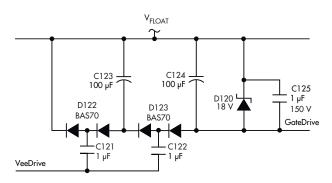

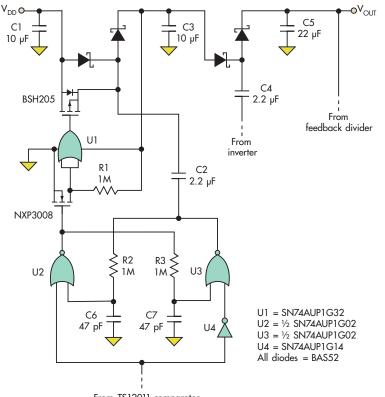

Figure 2 shows one of the four charge pumps using VeeDrive to provide a floating supply that follows a specific floating rail  $V_{FLOAT}$ . Because the gate drive must be at least 10 V below  $V_{FLOAT}$ , and some drops occur in the diodes, a two-stage

I. The I2-V downswitcher, which is already in the design, provides a square-wave to generate VeeDrive from V12 with about a 10-V swing.

2. The charge pump generates a robust supply that always tracks 15 V below V<sub>FLOAT</sub>, even if that voltage is below ground. The voltage also can be placed above V<sub>FLOAT</sub> by simply reversing the diodes and the polarized capacitors.

charge pump is employed. My actual design includes four copies of the charge pump shown in Figure 2 to produce GateDrive relative to each of four different floating supply rails. A single VeeDrive drives all four rails.

Starting with accumulators C123 and C124 discharged, when VeeDrive goes low (1 V), C121 charges up through C123 and the right half of dual diode D122 to approximately  $V_{FLOAT}$  – 1.5 V (after accounting for an approximate 0.5-V drop of the diode). When VeeDrive goes high (11 V), C121 discharges through the left half of D122 to  $V_{FLOAT}$  – 10.5 V (11 V – the 0.5-V drop in the diode). As cycling continues, charge continues to be drawn through C123, gradually charging up C123. In steady state, with no current being drawn off, C123 will charge up to 9 V, leaving its negative end at  $V_{FLOAT}$  – 9 V.

The second-stage charge pump, consisting of C122, D123, and C124, operates similarly to produce an additional 9-V offset. As a result, GateDrive is 18 V below  $V_{FLOAT}$ . In actual practice, of course, some current is being drawn off and there are more resistive drops, so the actual voltage settles close to 15 V. Should the voltage somehow exceed 18 V, Zener D120 clamps the voltage to no more than 18 V, which guarantees that the GateDrive's 20-V maximum limitation isn't surpassed. C125 helps to suppress switching noise caused by sudden loads on the supply during switching.

This arrangement can be readily adapted to many situations. If  $V_{FLOAT}$  can change, even fairly rapidly, the large size of accumulators C123 and C124 relative to flying capacitors C121 and C122 ensures that GateDrive maintains a fairly constant offset from  $V_{FLOAT}$ . This will hold true while the flying capacitors rapidly charge or discharge to the appropriate levels to continue the charge pump action.

Because the flying capacitors are ceramic (and thus unconcerned about polarity), GateDrive will remain 15 V below  $V_{FLOAT}$ , even if  $V_{FLOAT}$  should fall all the way to Logic GND or below. The flying capacitors must, however, have a sufficient voltage rating so that the highest value of  $V_{FLOAT}$  can occur in practice.

The output voltage at GateDrive is very consistent in practice and nicely matches the theoretical values after accounting for the various drops in the feed. There are several ways to adjust this voltage, though. Stages can be easily added to or removed from the charge pump to produce different multiples of the input voltage. If the input voltage is adjustable, finer granularity is possible.

It's easy to configure GateDrive when it must be above rather than below  $V_{FLOAT}$ . Simply flip the polarized accumulator capacitors to allow for the new state, and reverse the diodes. With those simple changes, the design will produce GateDrive at approximately  $V_{FLOAT}$  + 15 V.

STEVE HENDRIX is the principal engineer at Hx Engineering LLC. He has a BS in computer science and mathematics from the U.S. Air Force Academy.

#### WILLIAM SWANSON | swansontec@yahoo.com

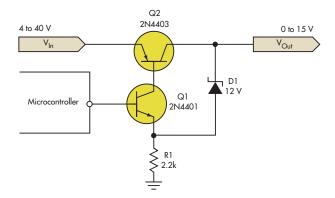

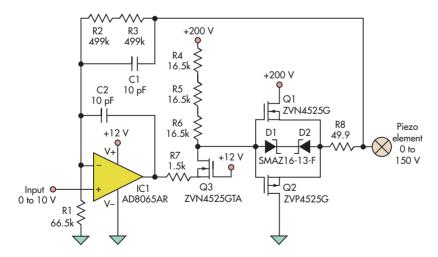

# High-Side Switch Provides Overvoltage Protection With Only Four Components

**ALTHOUGH MICROCONTROLLERS GENERALLY** run at low voltages, such as 3.3 V, they often need to control loads running at higher voltages like 12 V. If switching the low side isn't an option, the microcontroller needs a way to control a high-side switch from its low-voltage output.

The circuit in the figure provides a simple solution. Besides using few components, it provides overvoltage protection as a bonus. As long as the input voltage stays below approximately 15 V, the output voltage will equal the input voltage (minus the tiny  $V_{CE}$  drop across transistor Q2).

Once the input voltage exceeds that limit, however, the circuit begins acting as a low-dropout regulator (LDO), limiting the output voltage to 15 V. This feature is useful if the input voltage occasionally exceeds the rated load voltage, but the load switch needs to remain efficient otherwise.

Transistor Q1 and resistor R1 form a current sink. The microcontroller's output voltage ( $V_{OH}$ ) and Q1's base-emitter drop ( $V_{BE}$ ) create a stable voltage across the resistor, produc-

ing a current of  $(V_{OH} - V_{BE})/R1$ , or about 1.2 mA for a 3.3-V microcontroller. Most of this current flows through Q2's base,

The microcontroller turns the load off by controlling a high-side switch formed by Q1 and Q2. The current-sink action of Q1 controls the load voltage.

which controls the load. This current drops to zero when the microcontroller output goes low, switching the load off.

Zener diode D1 provides an alternative path for R1's current. If the diode's breakdown current is  $V_Z$ , it will begin to conduct when the output voltage exceeds  $V_Z + V_{OH} - V_{BE}$ , or about 14.6 V for a 12-V diode and a 3.3-V microcontroller. Since the voltage across R1 is constant, the diode effectively "steals" current from the base of Q2, reducing the amount of current flowing into the load. This negative feedback causes the circuit to act like a voltage regulator.

To apply this circuit to your application, adjust R1 so Q2's base current equals the maximum load current ( $I_{MAX}$ ) divided by Q2's gain ( $\beta$ ), or R1 =  $\beta \times (V_{OH} - V_{BE})/I_{MAX}$ . Be sure to select a transistor for Q2 that can dissipate the heat generated during an overvoltage event.

There is no straightforward way to calculate the exact output voltage, so the quickest approach is to try a few Zener diode

voltages and pick the one that works. A good starting point is to pick Zener voltage  $V_Z$  to equal to the desired output voltage minus the microcontroller voltage. This is just an overvoltage protector, so great accuracy should not be necessary.

If the overvoltage protection isn't important, simply remove the Zener diode. The resulting load switch uses only three components and retains the advantage of driving Q2's base with an actual current source. Even if the input voltage changes, Q2's base current remains constant.

WILLIAM SWANSON graduated in 2005 with a BSEE from Cal Poly San Luis Obispo. He currently designs boards and writes firmware for an early stage startup company.

VISHWAS VAIDYA | TATA MOTORS vmv74342@tatamotors.com

# Add Short-Circuit Protection, Diagnostics To Automotive High-Side/Low-Side Driver

**AUTOMOTIVE APPLICATIONS NEED** "smarter" drivers for their switches, which handle loads ranging from a fraction of an ampere to several amperes. Not only are these smart chips costly, but many times, they also aren't available for the 24-V applications used in this application area. Further, they usually come in quads and pairs, so designers are paying for unused switches.

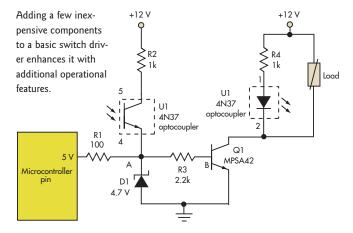

The simple circuit in the figure adds a few low-cost components to a "dumb driver" to make it a smart one, with added short-circuit protection and built-in diagnostics (*see the figure*). Transistor Q1 is an inexpensive driver that can withstand a few hundred volts and drive a few hundred milliamps. The microcontroller output goes high to latch the transistor on via the phototransistor of optocoupler U1. It next configures the output pin into an input, while U1 keeps the transistor on by supplying its base current through R2.

U1 has its LED in the load circuit of Q1 for detecting the short circuit. Under short-circuit conditions, it is "starved" of current, turning off the phototransistor driving power-switch Q1's base and protecting it. The CPU input pin can sample the occurrence of the short circuit at its convenience as needed, such as every few seconds.

The voltage at point A changes from a few hundred millivolts during short circuit to 4.7 V during normal operation, providing a clear indication to the CPU's input port. For retrybased recovery from short circuit, the CPU may turn itself into an output again at its leisure for restoring the "on" status and recovering the switch from its "trip-off" condition. The CPU pin again now goes into input mode to sense if the external

short is persisting. Depending on the application, a suitable retry regime can be worked out based on the end application.

During normal operation, the CPU can easily turn off the switch by pulling the output low. The CPU can issue a logic low by turning the pin into output again whenever it needs to switch Q1 off during normal operation.

VISHWAS VAIDYA is an assistant general manager of the electronics division at Tata Motors Ltd. He is based in Pune, India. He holds a master's degree in control engineering from the Indian Institute of Technology, New Delhi, India.

Vol. 2, No. 3

#### SPI Eases Interfacing For 5-By-5 Dot-Matrix Display

The circuit interfaces a display that features four 5-by-5 dot-matrix characters by using the display's serial peripheral interface and a programmable system on a chip (PSoC). The SPI reduces firmware overhead and enhances clock stability.

### Use An LED Dot-Graph Display To Complement Your DVM Readout

The digital voltmeter is a great tool, but it can show confusing results when the input voltage is unstable or erratic; by adding an auxiliary circuit driving a string of LEDs, you can easily also get a sense of the variations in input voltage.

#### Lamp Eliminates Need For Limit Switches In Flap-Motor Control

A flap controller needs current limiting to protect the motor when the flap reaches full closure. A small incandescent lamp can perform this task without the need for more costly limit switches or a microcontroller.

Do you have an Idea for Design for *Electronic Design*?

*Electronic Design* is always on the lookout for new ideas. Do you have one? Our Ideas for Design articles are short and to the point, often with a single figure or program listing to help explain the idea. If you would like to submit one, you can check out the details at

<u>https://www.electronicdesign.com/contribute.</u> We look forward to seeing your ideas.

GIRISH CHOUDANKAR | EMPHATEC INC., MARKHAM, ONT., CANADA gchoudankar@emphatec.com

# SPI Eases Interfacing For 5-By-5 Dot-Matrix Display

WHEN DISCUSSING DISPLAYS, seven-segment displays and LCDs are among the first that come to mind. Each type has its pros and cons. But generally, seven-segment displays cannot display letters, and LCDs tend to be bulky. Recently, I came across a four-character 5-by-5 dot-matrix, serial-input display (the SCDV5542 from Osram) that has several advantages.

The display can display alphanumeric characters and measures 10.16 by 19.91 mm (0.400 by 0.784 in.) with 3.12-mm (0.123-in.) characters. It has a serial peripheral interface (SPI) and allows high-speed data input. It features eight levels of dimming, an internal/external clock capability, and decoders, multiplexers, and an LED driver.

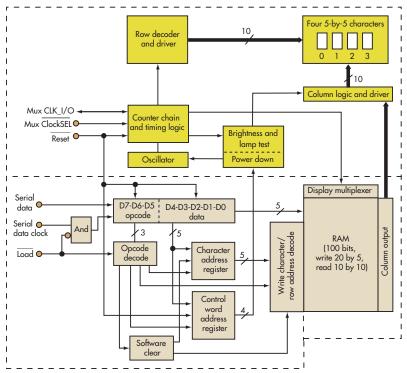

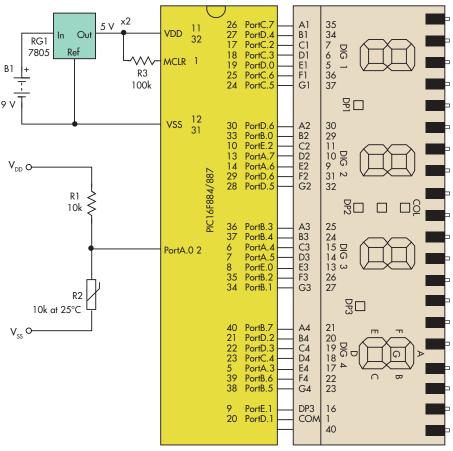

The device consists of a CMOS IC with control logic and drivers for the four 5-by-5 characters (*Fig. 1*). Each individual LED dot is addressable, so the user can create special characters. The device requires only four lines from a microcontroller. The IC accepts decoded serial data that is stored in

I. The SCDV5542 four-character 5-by-5 LED dot-matrix display stores decoded serial data in a 100bit internal RAM. Users can address each dot individually so they can generate custom characters.

internal RAM. Asynchronously, the RAM is read by the character multiplexer at the rate defined by the strobe.

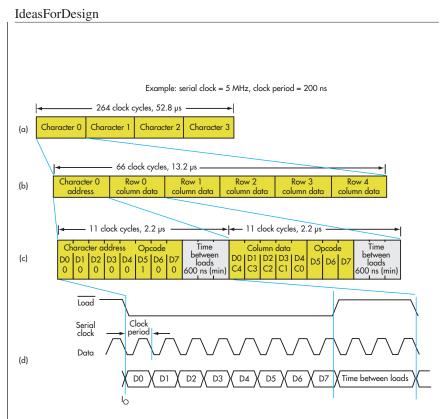

The microcontroller supplies a string of bit-mapped characters (*Fig. 2a, b, and c*). Each character consists of six 8-bit words. The first word is the character address. It's followed by the row data, which represents the on/off status of each LED in the column. Each bit of the 8-bit word consists of a 3-bit opcode (D7-D5) and 5 bits (D4-D0) of column data or character address or control word data.

To load data, bring the Load line low, which puts data in the serial register (*Fig. 2d*). The shift action occurs on the low-to-high transition of the serial clock (SDCLK). The least significant bit (D0) is loaded first. After one word is transferred, the Load line is set to high for opcode decoding. The decoded opcode latches D4-D0 in the character address register. The time between loads must be at least 600 ns. The character address register bits (D0-D4) and row address register bits (D7-D5)

direct the column data bits (D4-D0) to a specific RAM location.

The load character address tells the display the location (*Table 1*). The load column data controls the individual LED dot (*Table 2*). This feature allows you to create your own special symbols.

The display has seven brightness levels, defined by the percentage of full brightness that can be achieved: 100% (0xF0), 53% (0xF1), 40% (0xF2), 27% (0xF3), 20% (0xF4), 13% (0xF5), and 6.6% (0xF7). To control the brightness level, change the duty factor of the strobe pulse. Table 3 shows an example line.

In the power-down mode, the display brightness is set to 0% and the clock to the internal multiplexer is stopped, reducing the quiescent current,  $I_{CC}$ , to 50  $\mu$ A (*Table 4*). The display is reactivated by loading a new brightness level control word into the display. During power-down mode, data can be written to RAM.

Table 5 illustrates the operation of the lamp test mode, which sets all the LEDs to 53% brightness. This operation can be cleared by loading a brightness level control word.

Finally, the software-clear mode clears the address register and the RAM (*Table 6*). The

|    | TABLE 1: LOAD CHARACTER ADDRESS |    |    |       |          |     |           |     |             |

|----|---------------------------------|----|----|-------|----------|-----|-----------|-----|-------------|

|    | Opcod                           | Ð  |    | Charc | icter ac | Нех | Operation |     |             |

| D7 | D6                              | D5 | D4 | D3    | D2       | D1  | DO        | пех | load        |

| 1  | 0                               | 1  | 0  | 0     | 0        | 0   | 0         | AO  | Character 0 |

| 1  | 0                               | 1  | 0  | 0     | 0        | 0   | 1         | A1  | Character 1 |

| 1  | 0                               | 1  | 0  | 0     | 0        | 1   | 0         | A2  | Character 2 |

| 1  | 0                               | 1  | 0  | 0     | 0        | 1   | 1         | A3  | Character 3 |

#### TABLE 2: LOAD COLUMN DATA

|    | Opcod | e  |    | Co | lumn d | Or continue to and |    |                |  |

|----|-------|----|----|----|--------|--------------------|----|----------------|--|

| D7 | D6    | D5 | D4 | D3 | D2     | D1                 | DO | Operation load |  |

| 0  | 0     | 0  | CO | C1 | C2     | C3                 | C4 | Character 0    |  |

| 0  | 0     | 1  | CO | C1 | C2     | C3                 | C4 | Character 1    |  |

| 0  | 1     | 0  | CO | C1 | C2     | C3                 | C4 | Character 2    |  |

| 0  | 1     | 1  | CO | C1 | C2     | C3                 | C4 | Character 3    |  |

| TABLE 3: DISPLAY BRIGHTNESS |        |    |    |              |    |    |    |     |           |

|-----------------------------|--------|----|----|--------------|----|----|----|-----|-----------|

| (                           | Opcode | e  |    | Control word |    |    |    |     | Operation |

| D7                          | D6     | D5 | D4 | D3           | D2 | D1 | DO | Hex | load      |

| 1                           | 1      | 1  | 1  | 0            | 0  | 0  | 1  | F1  | 53%       |

| TABLE 4: POWER DOWN |       |    |              |    |    |    |     |           |               |

|---------------------|-------|----|--------------|----|----|----|-----|-----------|---------------|

|                     | Opcod | e  | Control word |    |    |    | Нех | Operation |               |

| D7                  | D6    | D5 | D4           | D3 | D2 | D1 | DO  | TICX.     | Level         |

| 1                   | 1     | 1  | 1            | 1  | 1  | 1  | 1   | FF        | 0% brightness |

| TABLE 5: LAMP TEST |       |    |              |    |    |    |    |     |                    |

|--------------------|-------|----|--------------|----|----|----|----|-----|--------------------|

|                    | Opcod | e  | Control word |    |    |    |    | Цах | Operation<br>Level |

| D7                 | D6    | D5 | D4           | D3 | D2 | D1 | DO | Hex | Level              |

| 1                  | 1     | 1  | 1            | 1  | 0  | 0  | 0  | F8  | Lamp test          |

|    | TABLE 6: SOFTWARE CLEAR |    |              |    |    |    |    |     |                    |

|----|-------------------------|----|--------------|----|----|----|----|-----|--------------------|

|    | Opcode                  | e  | Control word |    |    |    |    | Нех | Operation<br>Level |

| D7 | D6                      | D5 | D4           | D3 | D2 | D1 | DO | пех | Level              |

| 1  | 1                       | 0  | 0            | 0  | 0  | 0  | 0  | CO  | Clear              |

2. The bit-mapped characters supplied by the microcontroller occur within certain timing specifications. The times in this example are based on the use of a 5-MHz clock (a period of 200 ns).

display is blanked and the character register address is set to character 0. The internal counter and control word register are unaffected.

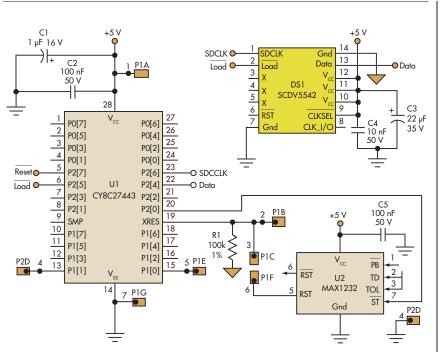

The example circuit uses a Cypress CY8C27443-24PXI programmable system-on-chip (PSoC) and a program written in C. I chose the PSoC because it enables designers to select individual hardware blocks. The serial interface to the display is straightforward and easy.

There are two ways to interface the display. The first is to connect a microcontroller via the serial port in mode 0. The serial port control register will be a simple shift register. Serial data enters and exits through the RXD pin, and the TXD pin outputs the clock.

The second method interfaces the display via the SPI in mode 0. Besides MISO (master in <u>slave</u> out) and clock, the display needs Reset and Load control lines. I chose SPI for this project because of its inherent advantages over serial port (*Fig. 3*). The circuit uses a MAX1232 as a reset controller, but you can choose any other method for properly resetting the microcontroller.

As noted, the PSoC enables you to choose your own hardware modules, which speeds development. For this project I opted for the SPI hardware instantiation to reduce firmware overhead. This choice also ensures the clock is stable and isn't influenced by other priority events.

Instantiating SPI simplified the display's communication block. Below is the flow chart for firmware implementation. (The code for the demo project can be downloaded from the online version of this article at *electronicdesign.com*.)

- Power up the display.

- Bring Reset low (for at least 600 ns) to clear the multiplex counter, address register, control word register, user RAM, and data register. The display will be blank. The display brightness will be set to 100%.

- If different brightness is desired, load the proper display brightness control word from Table 4.

- Load the character address into the display (*Table 1*).

- Load column data into the display (*Table 2*).

- Repeat steps 4 and 5 for rest of the digits.

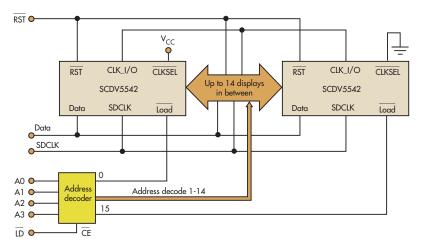

Finally, one display CLK\_I/O line can drive 15 slave CLK\_I/O lines, so you can cascade displays to increase the

3. The author opted to use a SPI instantiation for the display because it reduced the firmware overhead required.

4. The display's CLK\_I/O line can drive up to 15 slave CLK\_I/O lines, so designers can easily cascade multiple units.

project's display capabilities. Figure 4 shows the block diagram for interfacing multiple displays.

SOURCES 1. Osram SCDV5542 display, catalog.osram-os.com/media/\_en/ Graphics/00034132\_0.pdf

- 2. Cypress Semiconductor CY8C27443-24PXI, www.cypress. com/?mpn=CY8C27443-24PVXI

- 3. Cypress Semiconductor PSoC Designer, www.cypress.com/?id=2522

- Maxim Integrated MAX1232, www.maximintegrated.com/datasheet/index.mvp/ id/1286

GIRISH CHOUDANKAR works at Emphatec Inc., a Toronto-based design house for industrial control interfaces and switch-mode power supplies. He holds a bachelor's degree in electronics engineering from Mumbai University, India.

NEDJELJKO LEKIC AND ZORAN MIJANOVIC | UNIVERSITY OF MONTENEGRO, PODGORICA, MONTENEGRO

# **Use An LED Dot-Graph Display To Complement Your DVM Readout**

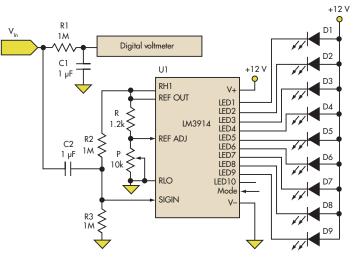

LEDS OFTEN ARE used to form a dot/bar graph display.<sup>1-4</sup> You also can use an LED dot-graph display as a complement to a digital voltmeter (DVM) with the LM3914 dot/bar display driver and nine LEDs.<sup>5</sup> This is useful where the input voltage is unstable, so the voltmeter indications are variable and the result is hard to read and understand.

By adding an associated circuit, the DVM measures and displays the approximate mean value of the input voltage, while the LED dot-graph provides information about the voltage's stability. This approach is suitable for rapidly testing power supplies.

The input signal passes through low-pass filter R1C1 to a digital voltmeter (Fig. 1). The filter's output is the mean value of the input signal, so the voltmeter indicates it is stable, and it is easy to read. (If the digital voltmeter has a built-in averaging option, the low-pass filter is not required.) Capacitor C2 passes the variable component of the input voltage to U1, and the LED dot graph that U1 drives indicates the intensity of these variations.

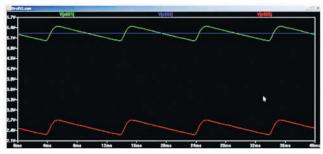

Figure 2 (obtained by simulation) shows how the low-pass REFERENCES and high-pass filters pass the mean and variable components of the input signal, respectively. If the input voltage is stable and doesn't have any ripple, only central LED D5 lights up.

As voltage ripples increase, the adjacent diodes begin to flicker. For larger ripples, more of the adjacent diodes light. Potentiometer P controls the LED dot-graph's sensitivity, with maximum sensitivity of 0.125 V when P is set to 0  $\Omega$ . Nine of the 10 available LED outputs are used.

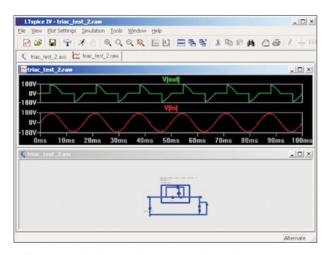

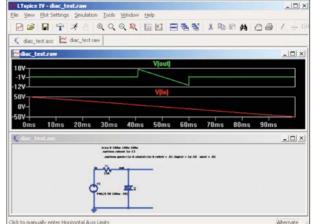

2. The simulation of the waveforms of  $V_{ln}$  (V[n001]) as well as the voltage at the low-pass filter output (junction of R1/C1) (V[n002]) and at the high-pass filter output (junction of R2/R3/C2) (V[n003]) show how the low-pass and high-pass filters pass the mean and variable components of the input signal, respectively.

I. The LED dot-graph display uses a standard display driver preceded by a high-pass filter. It visually complements a digital voltmeter's numeric output.

- 1. "LED bar-graph display represents two digits," Ajoy Raman, Bangalore, India, EDN, September 22, 2011.

- 2. "PIC microprocessor drives 20-LED dot- or bar-graph display," Noureddine Benabadji, University of Sciences and Technology, Oran, Algeria, EDN, September 1, 2006.

- 3. "Drive 16 LEDs with one I/O line," Zoran Mijanovic and Nedjeljko Lekic, University of Montenegro, EDN, June 9, 2011.

- 4. "Drive 12 LEDs with one I/O line," Charaf Laissoub, Maisons Alfort, France, EDN, February 4, 2010.

- 5. "LM3914 Dot/Bar Display Driver," National Semiconductor, February 2003, http://bit.ly/naDCR

NEDJELJKO LEKIC works at the University of Montenegro, Department of Electrical Engineering. He holds a PhD in electrical and computer engineering from the University of Montenegro. He has been working on designing identification systems based on RFID and/or biometrical identifiers as well as microcontroller systems for industrial automation.

ZORAN MIJANOVIC has been working as a professor with the electro-technical faculty at the University of Montenegro. He has designed many microcontroller devices for automation and control. He has a PhD in electronics from the University of Belgrade.

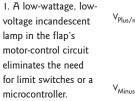

## Lamp Eliminates Need For Limit Switches In Flap-Motor Control

A FRIEND OF a friend asked me how to best open and close a flap at the end of a tube: pneumatics, hydraulics, electrical, or what? It was an automotive application and no hydraulic system or compressor was available. So, the answer seemed obvious: a 12-V dc, small-gear motor.

2. The lamp's current-voltage curve (vertical versus horizontal) illustrates the nonlinearity that makes this solution possible.

3. A plot of the circuit's operation shows the smooth, well-defined movement of the flap despite the variations in the motor's current.

The friend said he had tried that already, but he ran into problems with limit switches. The need for a constant closing force at the end of travel was another complication. Adding a microcontroller was too complicated, he said.

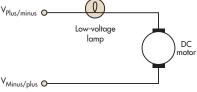

There seemed to be no simple answer. But eventually a solution came to me. And all it requires is a low-wattage, low-voltage incandescent lamp added to the motor circuit (*Fig. 1*).

The relationship between voltage and current in a small incandescent lamp is very nonlinear (*Fig. 2*). The tungsten wire in the lamp has a low resistance when cold. That's in the region up to around half a volt. Cursors CI and CII indicate that the slope in that region is 0.439/1.267 = 0.35, while the slope between the origin and CIII (nominal voltage and current) is 2.12.

> So, the lamp acts as an automatically changing resistor with a low resistance when the load is low and a resistance six times higher when fully loaded. That's exactly what we need to run an actuator without limit switches, microcontroller, transistors, or whatever.

> Figure 3 shows flap position, motor voltage, and motor current in a close/rest/open/rest/power-off cycle. The motor current's variations (red trace) reflect a badly aligned coupling and noise in the commutator. That is always present in small dc motors. But the motor used in this application is worse than most other motors in that respect. Despite that, the movement (grey) is smooth and well-defined.

> When the flap hits the mechanical stop (flap closed), the motor stops and the back electromagnetic field (EMF) drops to a low value, which means that current would have risen to perhaps five or 10 times the running current, depending on which motor and which supply is chosen. That, of course, would destroy the motor and is why limit switches and controllers are needed to switch off, or reduce, current.

> By adding a simple low-wattage and low-voltage incandescent lamp to the circuit, you can avoid this problem and keep the motor current at a low level that the motor can tolerate indefinitely. You can even use the lamp as a visual indicator that the flap has reached its closed (or open) position. And, the reduced current needed to keep the flap tightly closed comes without even asking for it.

GUNNAR ENGLUND, electrical engineer, worked with ABB and Siemens for many years and is now an independent consulting engineer. He is mostly active in research and problem solving regarding EDM in bearings (bearing currents).

Vol. 2, No. 4

#### Single-Cell Regulated Charge Pump Draws Low Quiescent Current

A charge pump (or Q pump) uses a flying-capacitor architecture to boost a single cell's voltage to a regulated 2.5V, yet operates at low quiescent current. This approach is a good fit for microcontroller applications where the load is usually in sleep mode and quiescent battery drain is more important than efficiency at higher loads. The two-stage design has efficiency in the 40 to 70% range—comparable to an LDO—yet consumes just microamps when the load is not active.

#### Hex Buffer, MOSFETs Build A High-Power, Lossless, Virtual Ground

This circuit uses a standard hex inverter to create an oscillator and Class-D amplifier, which in turn drives MOSFETs that can efficiently supply the bipolar rails and sink the ground current.

#### Graphical, Numerical Techniques Size LED Array's Drive

The nonlinear relationship between forward voltage and current in an LED makes it difficult to properly size the drive current and current-limiting resistor, but useful analysis can be derived from the exponential diode model.

Do you have an Idea for Design for *Electronic Design*? *Electronic Design* is always on the lookout for new ideas. Do you have one? Our Ideas for Design articles are short and to the point, often with a single figure or program listing to help explain the idea. If you would like to submit one, you can check out the details at

<u>https://www.electronicdesign.com/contribute.</u> We look forward to seeing your ideas.

# i constant in the second secon

## Single-Cell Regulated Charge Pump Draws Low Quiescent Current

BRUCE D. MOORE | ALERT SOLUTIONS CO., DAVIS, CALIF. bmoorealert@att.net

**CAPACITOR-BASED CHARGE PUMPS (OR** Q-pumps) generally aren't useful for sourcing large amounts of current, but they work well in niche micropower applications where space is at a premium. They work best in applications where the output voltages are integer multiples of the input voltage. The integer multiples, then, are operating points that result in peak efficiency.

However, Q-pumps can also work well when they are powered from a variable input such as a battery, particularly when quiescent battery drain is more important than heavy-load

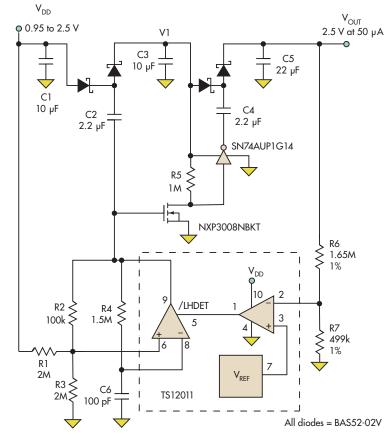

1. The low-voltage regulated charge pump uses the "flying capacitor" topology (C2 and C4) to "stack" and thus increase the output voltage.

efficiency. This might be the case when powering a microcontroller that spends most of its time in sleep mode.

Low-voltage microcontrollers such as those in the PIC24 or MSP430 families are generally powered from a regulated supply voltage such as 2.5 V. If clocked slowly, they might draw as little as  $25 \,\mu$ A or  $50 \,\mu$ A. In standby mode with only the real-time clock running, the current can be vanishingly small, often less than a microamp. This is a good application for the regulated two-stage Q-pump described here, which boosts a

single alkaline or nickel-metal-hydride (NiMH) cell to 2.5 V.

The "wings" of a Q-pump, called "flying capacitors," connect first to the input and then to the output. If the capacitor is stacked on the input voltage, it forms a voltage doubler. In the case of a regulated charge pump with a fixed output voltage, the voltage across the flying capacitor may differ significantly from the voltage across the output-filter capacitor.

When you connect two capacitors that are initially charged to different voltages, you get a spark or power dissipation in the switches as the capacitors equalize in voltage. This is why a simple voltage doubler typically exhibits better efficiency than a regulated Q-pump.

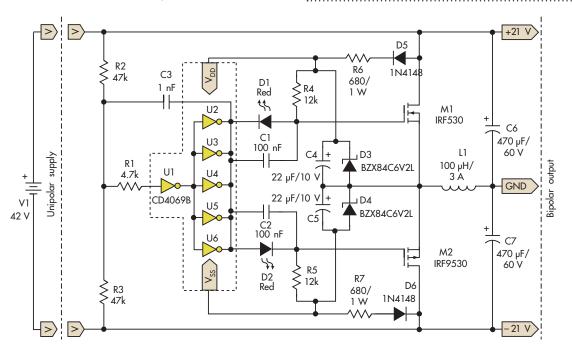

This regulated Q-pump has an on-demand oscillator, a feedback regulation loop made from an op amp and reference, and a two-stage pump circuit, plus two flying capacitors, C2 and C4 *(Fig. 1).* The first pump stage is driven directly by the Touchstone Semiconductor TS12011 comparator, which forms the oscillator, while the second stage is driven by an inverter powered from the output voltage of the first stage. The full-load efficiency varies from 70% to 40% over a 1- to 2.5-V input range, which is comparable to a linear regulator.

The TS12011 analog building block requires very low supply currents (3.2 µA typical) and

operates well down at the sub-1-V levels needed for singlecell operation. The comparator output stage has good drivecurrent capability down below 0.8 V V<sub>DD</sub>, which is an uncommon feature that allows us to drive the first stage directly from the oscillator.

The SN74AUP family of logic gates similarly uses super-low power. The MOSFETs were also carefully chosen for low-voltage operation, with low gate-threshold voltage specifications and low gate-charge characteristics for low switching losses. Using these high-performance components, the no-load quiescent current is a mere 8  $\mu$ A.

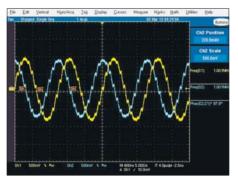

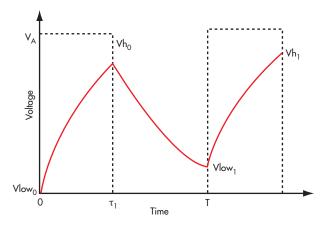

The RC oscillator is stopped when the output is in regulation via its /LHDET latch input (*Fig. 2*). When the output is above the regulation threshold set by the reference and feedback divider, the op-amp output drives the latch input low, latching the comparator output in the high state and stopping the oscillator.

A large hysteresis band was chosen for the oscillator, resulting in a large signal swing on the timing capacitor C6. This achieves the most efficient size-versus-current operating point for the oscillator. The maximum frequency is nominally set at 1 kHz with the component values shown, but can be adjusted up to about 3 kHz, where it becomes limited by the propagation delay through the comparator.

The amount of charge transferred with each cycle and the switching frequency determine the output current. Accurate calculations for the output impedance or output current from a regulated two-stage pump are complex and need a large spreadsheet, but you can make some oversimplifications to get into the right range. Assuming the capacitor is completely charged and discharged with each cycle (which obviously isn't true), then:

$$Q = C \times V$$

$$I = Q \times f$$

so:

$$I = C \times V \times F$$

where C is the flying capacitor value, V is the applied voltage during the charging phase, F is the oscillator frequency, and I is the output current you'd get if you could remove all the stored charge during the discharge phase (roughly equivalent to a short-circuit load current).

The modified Dickson Multiplier two-stage pump topology used here is a quadrupler, and both stages must be designed to transfer the needed amount of charge at the worst-case lowbattery voltage. The first stage is the most important, because the voltage applied to the capacitor is low. Any drop across the first rectifier subtracts from the applied voltage with a result-

2. The oscillator controls how much charge is pumped and thus the output voltage:  $V_{OUT}$  (top waveform), comparator output (middle), and op-amp output (bottom).

ing loss in headroom, a problem when trying to multiply up to 2.5-V output levels.

The rectifier choice is further complicated in this low-quiescent application by leakage currents, which effectively load down the pump and increase idling current. The BAS52-02V Schottky diode has a good combination of low reverse leakage, low forward drop, small packaging, and wide availability.

Reverse leakage current at high temperature is the weakness of Schottky diodes, but lab measurements show that the typical BAS52 is very good on this parameter, at less than 1  $\mu$ A at 50°C. For even lower reverse leakage, there is the BAS40-02V, but the tradeoff is about 75-mV higher forward-voltage drop.

The capacitor values and switching frequency are chosen to be somewhat excessive for charge transfer, so they don't get in the way of the voltage-drop/headroom issues. As a result, the frequency is low and the capacitors are relatively large, which also keeps switching losses in check. More importantly, a long on-time allows the voltage across the diode to reach a minimum, with the tail end of the forward voltage/current curve being a little less than 0.2 V for the BAS52.

From the simplified charge-transfer equations above, an overly optimistic estimate for first-stage current is:

$$(V_{DD} - V_{FWD} - V_{SAT1}) \times C3 \times F =$$

(0.95 V - 0.2 V - 0.05 V) × 2.2  $\mu$ F × 1 kHz = 1.5 mA

which is more than sufficient to meet a  $50-\mu$ A load-current requirement. The best-possible peak-output voltage that you can achieve for the intermediate V<sub>1</sub> tap is:

$$2V_{DD} - 2V_{FWD} - V_{SAT1(high)} - V_{SAT1(low}$$

Similarly, the second-stage peak voltage for V<sub>OUT</sub> is:

From TS12011 comparator

3. To achieve operation below 0.9 V, the first stage is modified by adding a synchronous rectifier across the first diode.

$$2V_1 - 2V_{FWD} - V_{SAT2(high)} - V_{SAT2(low)}$$

Thus, the best-possible peak-load voltage at the minimum input voltage is:

$V_{OUT} = 4V_{DD} - 4V_{FWD} - 4V_{SAT} = $$(4 \times 0.95 \text{ V}) - (4 \times 0.2 \text{ V}) - (2 \times 0.05 \text{ V}) - (2 \times 0.1 \text{ V}) = 2.7 \text{ V}$$$

where  $V_{SAT1}$  and  $V_{SAT2}$  are the voltage drops across the comparator and the AUP inverter output stages in the ON state, respectively. Again, this analysis is oversimplified but points out the limits of operation.

This math shows that there is not a lot of room for temperature variation and component tolerances when trying to

**BRUCE D. MOORE** is a consulting analog engineer for Alert Solutions Co., doing new product definition and application circuit development for amplifier and power-supply ICs. He graduated with a BSEET from Heald Engineering College, San Francisco. quadruple the lower end of the voltage range of a single cell. We can improve this, and get to sub-0.9 V operation, by several means: adding another pump stage; changing the output voltage to 2.2 V (but the microcontroller may not be able operate this low); or adding a synchronous rectifier across the first diode.

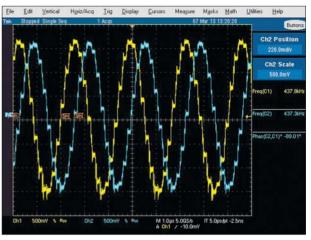

The third option is chosen here, due to its good efficiency at the operating "sweet spots" (*Fig. 3*). A low-threshold P-channel MOSFET with low gate charge shunts the first pump diode, reducing the forward drop from 0.2 V to approximately 0.01 V. This adds a few hundred extra millivolts right at the front end, where it's needed most.

A NOR-based logic circuit provides nonoverlapping gate-drive signals to the synchronous switch. The goal is to be certain that the MOSFET gate is never driven high when the flying capacitor is high. The amount of dead time is set by the 1 M $\Omega$  × 47 pF RC time constants. Here, the dead time is very long since the 1-kHz oscillator is so slow.

Charge pumps offer an alternative to inductor-based boost regulators and can fit nicely with the dual nature of many microcontroller loads, with their low-current RTC mode versus heavier but infrequent run mode. The challenge

of designing them for low input voltages can be met by using the right low-voltage components, choosing sensible switching frequencies, and taking full advantage of the V-I characteristics of the rectifiers.

## **IDEAS FOR DESIGN WANTED**

Send us your Ideas For Design. We'll pay you \$150 for every Idea For Design that we publish. In addition, this year's top design as selected by our readers will earn an additional \$500, with two runners up each receiving \$250. You can submit your Ideas For Design via:

• E-mail: joe.desposito@penton.com

OR BY

- Postal mail to: Ideas For Design

Electronic Design

1166 Avenue of the Americas, 10th Floor

- New York, NY 10036

- Go to www.electronicdesign.com for our submission guidelines.

## Hex Buffer, MOSFETs Build A High-Power, Lossless, Virtual Ground

LOUIS VLEMINCQ | BELGACOM, EVERE, BELGIUM louis.vlemincq@belgacom.be

A VIRTUAL GROUND IS useful whenever you need to create a bipolar supply but the dc source is unipolar, as is often the case with battery-operated equipment. Sometimes, the solution is as easy as using a high-ohm resistive divider to provide a mid-supply potential. But if the ground impedance needs to be lower, the simple approach can be enhanced by using a buffer amplifier.

When the ground created this way sees high imbalance currents, though, things become more complicated. The buffer not only needs to be a power buffer, it will also have to dissipate the result of any imbalance. This is wasteful, and it may even require bulky, inconvenient heatsinks.

This circuit addresses these issues simply, cheaply, and effectively (*see the figure*). It retains the resistive divider plus buffer configuration, but with a big difference. The buffer is now a self-oscillating Class D amplifier, capable of providing many amperes of ground current and of "recycling" any imbalance back to the supply. The circuit is compact and efficient, while providing a stiff, accurate, and powerful ground.

The oscillator is built around a simple CD4069 CMOS hex buffer. Most of its inverters act as gate drivers for the power MOSFETs. Inverter U1 provides the non-inverting input of the amplifier, as the inverting input is implicit and is represented by the CD4069's mid-supply potential. Capacitor C3 provides positive feedback and allows the circuit to self-oscillate.

The entire control circuit has a floating supply referenced to the output. Diodes D3 to D6 and resistor pair R6/R7 generate this supply from the dc input. R2 and R3 create the virtual ground potential. In this example, they are equal, as will generally be the case, but asymmetrical supplies also can be created.

For greater accuracy, a trim potentiometer can be added to the midpoint of R2/R3. With the values shown, the pulsewidth modulation (PWM) frequency is approximately 45 kHz, which can be modified by changing C3.

The power MOSFETs and inductor must be sized according to the expected output current. If a very clean ground is required, an additional LC filter can be used after L1 and C6/ C7 to clean up the remaining switching residues.

**LOUIS VLEMINCO** works as a design engineer in Physcial Layer Engineering at Belgacom, Evere, Belgium.

Although it requires more components than the conventional resistor-divider approach, this Class D oscillator/amplifier (based on a CD4069 hex inverter) drives power MOSFETs that make the virtual ground much more efficient.

# ICICS for design

### Graphical, Numerical Techniques Size LED Array's Drive

KENG WU | SWITCHING POWER INC. kengchi.goah@gmail.com

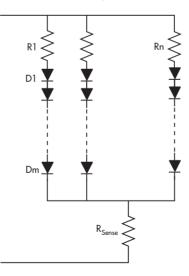

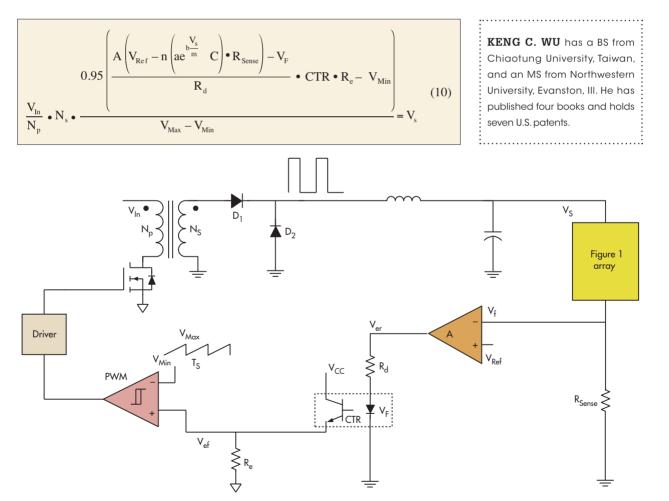

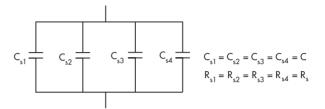

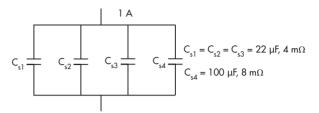

**LED-BASED LIGHTING IS REPLACING** incandescent and gas-discharge lamps in many situations. As practical lighting sources, and considering their directional nature, LED fixtures usually use multiple LEDs arranged in an array, with "m" LEDs in a serial string and "n" such strings in parallel (*Fig. 1*). For the array configuration and the exponential I-V characteristics model of a single LED,<sup>1</sup> it's additionally possible to have a similar model representing the loading of such an array.

Since the single LED is a diode with a nonlinear forward-voltage/current, driving it with a fixed voltage source is generally not recommended. Rather, a serial (current-limiting) resistor is needed to equalize the power source and the load (*Fig. 2*). However, sizing this resistor requires a significant analytical manipulation. Using the single-LED exponential model, a Kirchoff's voltage law (KVL) equation around the circuit loop gives:

$$R_x \left( a e^{bV_F} + c \right) + V_F = V_s \quad (1)$$

which can be rearranged to:

$$R_x = \frac{V_s - V_F}{ae^{bV_F} + c} \quad (2)$$

where a, b, and c are model parameters for a selected LED, as defined in the reference.

This is a challenge to solve symbolically, but it can be solved numerically with mathematical software tools. Alternatively, it can be solved graphically by separating the two key I-V relationship equations,  $v + R_x I_F = V_s$  and  $I_F = ae^{bv} + c$ .

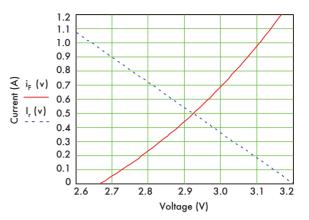

For example, using a Lumileds Luxeon Rebel ES LED with a 3.2-V dc source and a desired drive current of 0.5 A, the horizontal current line intercepts the LED curve at 2.92 V (*Fig. 3*). Therefore, the series resistor will be  $R_x = (3.2 - 2.92)/0.5 = 0.56 \Omega$ .

However, the graphical approach would not handle an LED array effectively, and the numerical method works better. To represent the array current  $i_A$ , the exponential model for the (m × n) array is modified, since voltage drops across current-limiting resistor  $R_n$  and sense-resistor  $R_{Sense}$  are usually small compared with driving-source  $V_s$ :

1. Establishing the correct resistor size for each string of an array of n strings, where each strings has m LEDs, is challenging due to the nonlinear nature of the diodes.

$$i_A = n \left( a e^{b \frac{V_s}{m}} + c \right)$$

(3)

With the array model, the switchmode buck-regulating current driver in a closed-loop configuration (*Fig. 4*) can be described by a set of equations starting at the feedback point, circling around the control loop, and ending at the driver output:

• Current sensing:

$$V_f = i_A \bullet R_{Sense}$$

(4)

• Error amplifier:

$$V_{er} = A(V_{Ref} - V_f) \quad (5)$$

• Effective error:

$$V_{ef} = \frac{V_{er} - V_F}{R_d} \bullet CTR \bullet R_e \quad (6)$$

• PWM ramp:

$$V_{\text{Ramp}}(t) = V_{\text{Min}} + \frac{V_{\text{Max}} - V_{\text{Min}}}{0.95 \bullet T_{\text{s}}} t$$

(7)

2. Even for a single LED driven by a voltage source, the exponential current-voltage relationship complicates selection of the series-resistor value.

• Duty cycle, D:

$$V_{Ramp}(D \bullet T_s) = V_{ef}$$

(8)

• Power stage:

$$\frac{V_{In}}{N_{p}} \bullet N_{s} \bullet D = V_{s} \quad (9)$$

With effort, all the equations can be consolidated into a single, closed-loop equation. Equation 10 is a transcendental equation with an exponential term that prevents us from solving it analytically, but it can be solved using computational techniques and software tools.

#### Reference

1. "Generate Realistic Models for LED Current Versus Voltage," Keng C. Wu; Electronic Design, Vol. 61, No. 1, p. 52, Jan. 10, 2013, http://electronicdesign.com/power/generate-realistic-models-led-current-versus-voltage

3. The intersection of the desired current line and the forward current/voltage curve (red) leads to the unique solution to the nonlinear equations of the LED model. (The blue line is the reverse-bias current/voltage relationship.)

4. Analysis of the switch-mode buck-regulating current driver in a closed-loop configuration for driving an array yields a set of equations that are better solved using numerical computation rather than an analytical, closed-form approach.

Vol. 2, No. 5

# Simple Addition Permits Voltage Control Of DC-DC Converter's Output

This article presents apples-to-apples test results for noise densities for several low-noise discrete, SMT n-JFETs. The tests used the same operating conditions so that designers can make a fair comparison for their applications.

# Simple NiCd Battery Charger Includes Charge Indication

This circuit uses a microcontroller and simple algorithm managing voltage regulator ICs and discrete components to control charging of nickel-cadmium batteries. It provides a steady charging current matched to the battery capacity while avoiding overcharging; it also includes LEDs that indicate the status of the charging process to the user.

Do you have an Idea for Design for Electronic Design? *Electronic Design* is always on the lookout for new ideas. Do you have one? Our Ideas for Design articles are short and to the point, often with a single figure or program listing to help explain the idea. If you would like to submit one, you can check out the details at

<u>https://www.electronicdesign.com/contribute.</u> We look forward to seeing your ideas.

# ICOC For design

## Simple Addition Permits Voltage Control Of DC-DC Converter's Output

EUGENE PALATNIK | ITEC ENGINEERING epalatn@itecengineering.com

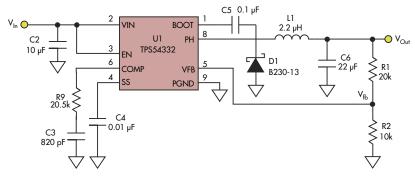

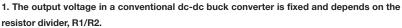

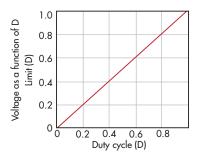

**IN A STANDARD DC-DC** converter, a resistor divider typically defines a fixed output voltage. However, applications like programmable output voltage power supplies and motor control circuits require dynamic control of the dc-dc converter's output voltage. The circuit described here allows control of the converter's output voltage,  $V_{Out}$ , with a control voltage,  $V_{C}$ .

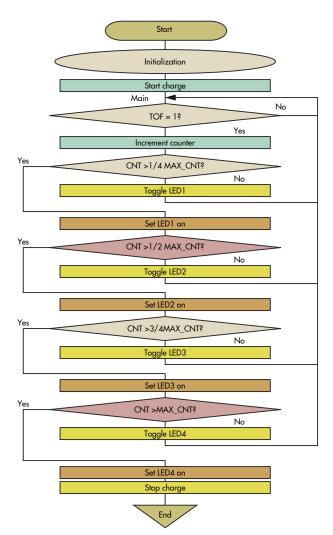

In a conventional dc-dc buck converter,  $V_{\text{Out}}$  is:

$$V_{\text{Out}} = V_{\text{fb}} \left( \frac{\text{R1} \quad \text{R2}}{\text{R2}} \right) \quad (1)$$

so V<sub>Out</sub> is fixed by the values of R1 and R2 (*Fig. 1*).

The added circuitry in Figure 2 enables users to control the same dcdc converter's output voltage using  $V_{C}$ . In this case, R2 is not connected to the ground but, rather, to  $V_{r}$ . Equation 1 then becomes:

2. The added circuitry in this version of the dc-dc converter permits control of  $V_{Out}$  by varying a control voltage,  $V_C$ .

$$V_{Out} - V_r = \left(V_{fb} - V_r \left(\frac{R1 R2}{R2}\right) \right)$$

(2)

Since  $R1 = 20 \text{ k}\Omega$  and  $R2 = 10 \text{ k}\Omega$ , Equation 2 can be simplified to:

$$V_{Out} - V_r = 3(V_{fb} - V_r)$$

(3)

or:

$$V_{Out} = 3 V_{fb} - 2 V_r$$

(4)

R3 and R4 have the same value, 10  $k\Omega$ , so amplifier U2's output voltage is:

$$V_r = 2 V_{Ref} - V_C \quad (5)$$

where V<sub>Ref</sub> is the reference voltage generated by U3 after resistor divider R7/R8.

Combining Equation 4 and Equation 5:

$$V_{Out} = 3 V_{fb} - 4 V_{Ref} + 2 V$$

(6)

To simplify Equation 6, choose components that make:

$$3 V_{fb} = 4 V_{Ref} \quad (7)$$

Then Equation 6 becomes:

$$V_{Out} = 2 V_C \quad (8)$$

The internal voltage reference of U1 is 0.8 V. By choosing R7 = 10 k $\Omega$  and R8 = 3.16 k $\Omega$ , V<sub>Ref</sub> = 0.6 V, satisfying Equation 7.

Finally, C1 lowers U2's output impedance at high frequencies, maintaining the stability of U1's feedback loop.

The added circuitry allows users to control the buck converter's output voltage,  $V_{Out}$ , in the range of 0 to 5 V with a control voltage,  $V_C$ , in the range of 0 to 2.5 V. Similar circuitry can be designed

**EUGENE PALATNIK** is an electrical engineer and president of ITEC Engineering LLC. He is active in the design of electronics for medical, scientific, and industrial applications. be designed for use with a boost converter, or any other dc-dc converter, as long as its feedback voltage pin is accessible.

### Simple NiCd Battery Charger Includes Charge Indication

ABEL RAYNUS | ARMATRON INTERNATIONAL INC. abelr@armatronintl.com

**RECHARGEABLE NICKEL-CADMIUM (NICD) BATTERIES** are widely used in consumer electronics because of their high energy density, long life, and low self-discharge rate. Standard NiCd cells can be charged at different rates: a fast charge with high current, or overnight with low current.

Regardless of the charge speed, a steady current should be provided to

the battery during charging. Also, more energy must be supplied to the battery than its actual capacity to compensate for energy loss during charging.

However, two problems must be addressed when designing a charger for them: how to set the proper charging-current value, and how to stop the charging process when the battery is

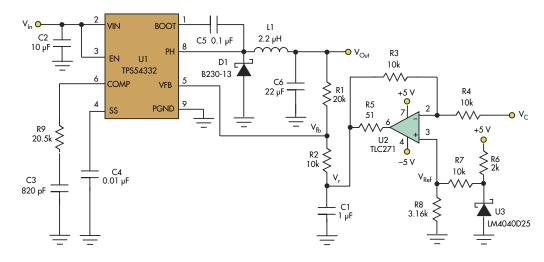

1. The constant charging current is produced by an LDO and resistor and gated by Q1, which in turn is managed by an output of the microcontroller. A quartet of LEDs, also microcontroller-driven, indicates charge status to the user.

full, to avoid overcharging. This simple and inexpensive charger overcomes both problems. The cheapest and safest way to charge a NiCd battery is to charge at 10% of its rated capacity per hour for 16 hours. The battery pack used contained two AA-size 1200-mAh NiCd cells, so the battery should be charged with 120-mA current.

In the charging circuit of Figure 1, a constant charge current is generated by a current regulator comprising IC3 (an LM317 LDO) and resistor R3, where R3 is 1.25 V/120 mA, about 10  $\Omega$ . Switching MOSFET Q1 (IRF520) was chosen because of its very low open-state (conductive) impedance of 0.3  $\Omega$ .

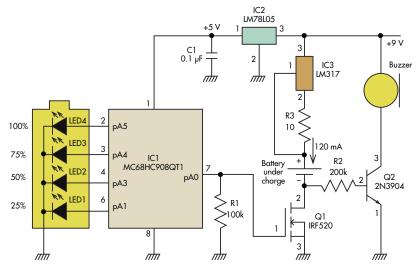

The best charging practice is to use a timer to prevent overcharging to continue past 16 hours. This approach does not require an end-of-charge sensor, and it ensures a full charge. The timing function is performed by microcontroller IC1, which also reports the state of charge via the LEDs.

Any microcontroller could be used in this project. Here, the inexpensive eightpin Motorola (Freescale) MC68HC-908QT1 microcontroller was used. Each charging step is indicated by lighting a corresponding LED. The number of steps is determined by the number of available outputs of the microcontroller, without adding any extra components. Since the microcontroller has five outputs, one of them is used for charge triggering, and so the four can be used for charge indication. To minimize the number of components, LEDs with built-in resistors are used (WP710A10YD5V, www.kingbrightusa.com).

To make the process more visual, these LEDs should be located in line with the outline of the battery drawn around them, so lighting the LEDs one by one will clearly indicate the progress of charging. It is reasonable to choose the time intervals to be equal, with the LEDs indicating 25%, 50%, 75%, and 100% of battery-charge time.