# N E T W O R K DESIGNALS

Frequently Asked Questions:

## **ETHERNET MAC AND PHY**

William Wong, Embedded /Systems /Software Editor

#### How do you implement a single-chip Ethernet microcontroller?

The trick is to incorporate the microcontroller, Ethernet MAC, and PHY on a single chip, thereby eliminating most external components. This enables the MAC and PHY to be matched and reduces the overall pin count and chip footprint. It can also lower power consumption, especially if powerdown modes are implemented.

#### What is an Ethernet MAC?

The MAC is the media access controller. The Ethernet MAC is defined by the IEEE-802.3 Ethernet standard. It implements a data-link layer. The latest MACs support operation at both 10 Mbits/s and 100 Mbits/s. This crop typically implements the MII.

#### What is the MII?

The Media Independent Interface (MII) is an Ethernet industry standard defined in IEEE 802.3. It consists of a data interface and a management interface between a MAC and a PHY (Fig. 1). The data interface consists of a channel for the transmitter and a separate channel for the receiver. Each channel has its own clock, data, and control signals. The MII data interface requires a total of 16 signals. The management interface is a two-signal interface—one signal for clocking and the other for data. With the management inter-

ISO network model Ethernet Flow Application MAC control Presentation Transmitter Receive buffers buffers MII Software Session management Transmitter Receiver (RPC) 1 Medium-independent interface (MII) Transport (TCP/UDP) Medium-independent interface (MII) Ethernet 1 Network PHY **10BaseT** 100BaseTX (IP) Transmitter Transmitter Loopback Data link support (MAC) Receiver Receiver Hardware Phase-locked Manchester 4B/5B Physical loops encodina encodina (PHY)

1. The Ethernet MAC and PHY implement the bottom two layers of the International Organization for Standardization/Open System Interconnect (ISO/OSI) stack. The MAC interfaces with the PHY through an MII. The typical 10/100 PHY Ethernet implementation incorporates separate 10BaseT and 100BaseTX interfaces.

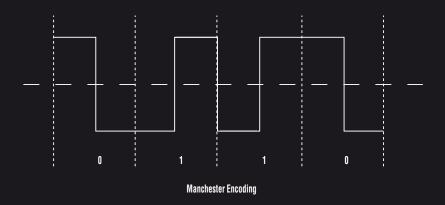

2. Manchester Encoding requires transitions up to twice the frequency of data throughput, but it allows easy clock synchronization.

face, upper layers can monitor and control the PHY.

#### What is an Ethernet PHY?

The PHY is the physical interface transceiver. It implements the physical layer. The IEEE-802.3 standard defines the Ethernet PHY. It complies with the IEEE-802.3 specifications for 10BaseT (clause 14) and 100BaseTX (clauses 24 and 25).

#### What's so hard about putting an Ethernet PHY on the same chip as the MAC?

The PHY incorporates a signifi-

cant amount of analog hardware, while the MAC is typically an alldigital component. The chip footprint and the mixed analog/digital architecture are why MACs were first incorporated in microcontrollers, leaving the PHY off-chip. More flexible, higher-density chip technology has allowed both the MAC and PHY to reside on the same chip.

#### Are external components other than the RJ-45 jack still required?

Yes. The PHY provides most of the analog support, but the typical implementation still requires a half-dozen discretes and a localarea network magnetics isolation module. The latter is typically a 1:1 ratio transformer. These primarily protect the PHY from electrical abuse.

#### Why are the 10BaseT and 100BaseTX PHY implementations different?

The packet description for both implementations is essentially the same, but the signaling mechanism for the two is completely different. This prevents one hardware implementation from easily handling both speeds. The 10BaseT uses Manchester encoding, while the 100BaseTX uses 4B/5B encoding.

#### What is Manchester Encoding? Manchester Encoding, also called

Manchester Encoding, also called Manchester Phase Encoding, implements each bit as a phase change (*Fig. 2*). A "1" is normally a rising edge in the middle of a cycle, while a "0" is a falling edge. A transition at the end of a cycle is ignored and may be required depending upon the prior bit value.

#### What is 4B/5B encoding?

4B/5B encoding is one of many block coding methods. It takes a 4bit block and encodes it into a 5-bit block. This allows the 5-bit block to always have at least two "1" transitions so clock synchronization will always be possible within a 5bit block. The approach imposes 25% overhead. ED Online 9177

### THE INDUSTRY'S FIRST SINGLE-CHIP FAST-ETHERNET FLASH MICROCONTROLLER

#### MC9S12NE64 Single-Chip Fast-Ethernet 16-Bit Flash Microcontroller

Based on the powerful HCS12 core, the MC9S12NE64 combines the following features, enabling design engineers to overcome the high costs, slow development times, and inherent complexities of existing multichip Ethernet offerings.

- 25-MHz HCS12 core

- 64-kbyte flash

- 8-kbyte RAM

- 8-channel, 10-bit analog-to-digital converter

- Two-channel, 16-bit timer

- 10/100 EMAC

- 10/100 EPHY

- 2 SCIs, SPI, and  $I^2C$

- Up to 70 GPIO

- Available in 112-pin LQFP and 80-pin TQFP-EP

#### MC9S12NE64 Demonstration Board (DEM09S12NE64)

The MC9S12NE64 demonstration board has all the required components, including the device itself, switches, LEDs, a potentiometer, an Ethernet port, a universal power supply, access to user I/O via the MCU breakout header, and software demos with application code. The CodeWarrior tools are included, too, as well as a preprogrammed flash monitor. Get started using the 9S12NE64 by testing its features, and get hands-on experience by using the part to monitor and control devices remotely by using an Ethernet connection. Everything to get you started writing and debugging code is all available now for only \$74.95 (USD). Visit www.freescale.com/NE64.

DEM09S12NE64

Fully functional Web server (AN2759)